# CML Semiconductor Products PRODUCT INFORMATION

FX013 HSC Tone Decoder for 'Pagers

## Features

- 'N'-Tone HSC Decoding

- EIA and CCIR Tonesets

- 4-Bit Parallel (HEX) Data Output

- µProcessor Interface

- Auxiliary 23.33kHz Clock Output

- Low-Power (2.5V @ 500µA<sub>MIN</sub>) Requirement

Publication D/013/1 February 1993 Provisional Issue

- Radiopaging, PMR Selcall and Remote Signalling Applications

- Selectable 560kHz or 4.48MHz Xtal/Clock Operation

- Automatic Power-Up Reset Facility

- 24-Pin/Lead Package Versions

# Brief Description

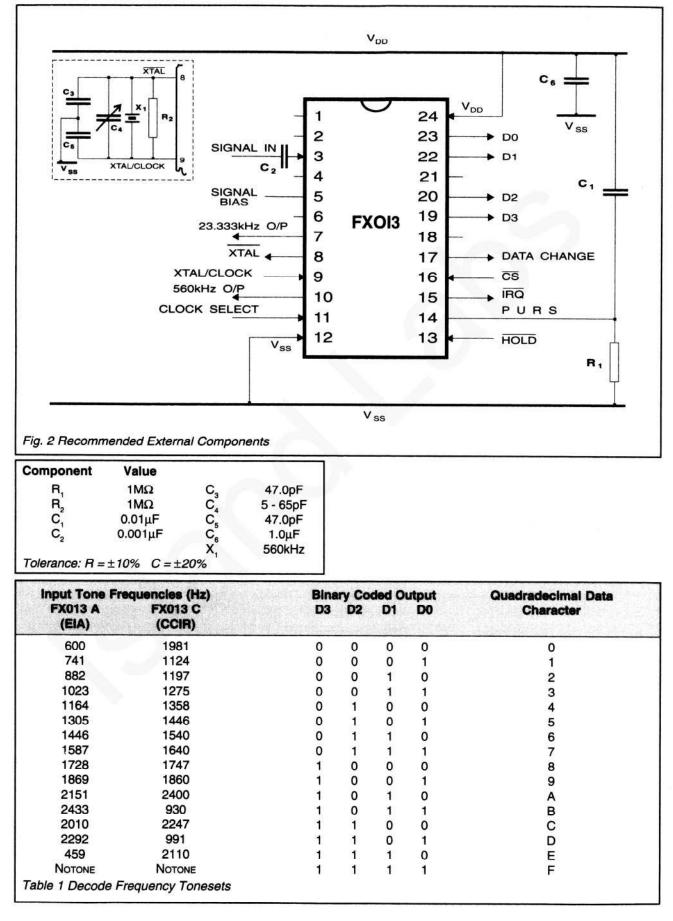

The FX013 is a very low-voltage continuous "N"-Tone EIA and CCIR HSC tone decoder which is ideal for tone-paging applications.

From an analogue signal input the FX013 will produce a representative 4-bit (HEX) parallel output word for either toneset. Hold, Data Change and Interrupt features combined with the 4-bit data output enable µProcessor interface and control. Alternatively, the FX013 may be used in a simple passive system using the Data Change and Data Outputs

This device can be used with a customer specified µProcessor or with a pre-programmed address decoder/display driver. The FX013 has on-chip automatic Power-Up Reset circuitry, which with selected time-constant components ensures the correct start-up settings for most supply conditions, making this device ideal for installation within radiopaging units.

Operating at 2.5 volts with a minimum current requirement of  $500\mu$ A, the FX013 is available in two toneset versions to decode either EIA (A) or CCIR (C) tones.

To cater for variations in design requirements the FX013 is produced in both 24-pin cerdip DIL and plastic quad packages.

## **Pin Number**

•

# Function

٦

| FX013J/LG             |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

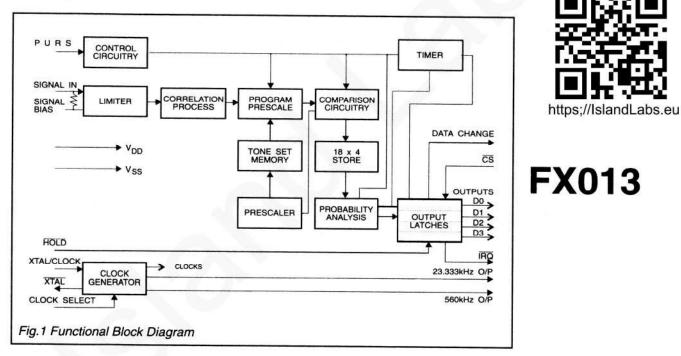

| 3                     | <b>Signal In:</b> HSC input tones are a.c. coupled to this pin; dc bias of the internal high gain limiter is set up by an internal $3M\Omega$ bias resistor connected between this pin and the Signal Bias pin. Neither pin should be loaded with any other circuitry.                                                                                                                                                                                |

| 5                     | Signal Bias: See Signal In.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7                     | <b>23.33kHz</b> Clock <b>Out:</b> A 23.333kHz buffered squarewave logic output directly derived from the oscillator frequency (nominally 560.0kHz). This pin may be used for auxiliary functions, e.g. external timing of received tone periods and for other '03 series devices.                                                                                                                                                                     |

| 8                     | Xtal: Output from on-chip inverter.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 9                     | <b>Xtal/Clock:</b> Input to on-chip inverter. May be used in conjunction with the Xtal O/P and a 560kHz ceramic resonator/trimming capacitor, or a 4.48MHz Xtal Circuit. May also be used with a buffered input from an externally derived 560kHz or 4.48MHz clock.                                                                                                                                                                                   |

| 10                    | 560kHz Buffered O/P: A buffered 560kHz signal is output from this pin.                                                                                                                                                                                                                                                                                                                                                                                |

| 11                    | <b>Clock</b> Frequency <b>Select:</b> Normally at logic "1" if a 560kHz resonator is being used. If held at logic "0," a divide by 8 function is switched in after the oscillator circuit to divide down the 4.48MHz frequency to 560kHz. This pin has an internal $1M\Omega$ pullup resistor.                                                                                                                                                        |

| 12                    | V <sub>ss</sub> : Negative Supply (GND).                                                                                                                                                                                                                                                                                                                                                                                                              |

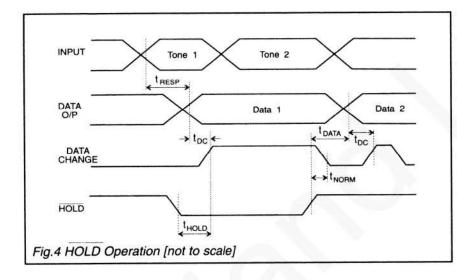

| 13                    | <b>Hold I/P:</b> If taken to V <sub>ss</sub> and a tone is input, the resulting Data Change output latches to logic "1" and the Data lines output the code for the detected tone regardless of subsequent changes to the input tone, until Hold is returned to $V_{DD}$ . This facilitates interrupt/handshake routines for $\mu$ Processors when used in conjunction with the Data Change O/P. This pin has an internal 1M $\Omega$ pullup resistor. |

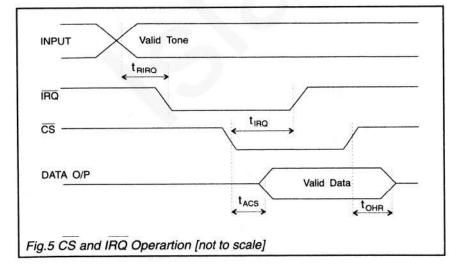

| 14                    | <b>Power-Up Reset (P U R S):</b> To reset internal circuitry on power-up, a logic "1" is required at this pin for a duration of at least 1.0ms after clock is applied. For slow-rising supplies the time constant recommended by the components in Figure 2 should be increased accordingly.                                                                                                                                                          |

| 15                    | <b>IRQ:</b> Interrupt Request. This output, is latched to logic "0" when a tone is detected and the CS pin is at $V_{_{DD}}$ , i.e. chip disabled. This pin is reset to logic "1," enabling its for use in wire-ORing with similar outputs from other peripherals. This pin has internal 1k $\Omega$ pulldown and 100k $\Omega$ pullup resistors on-chip.                                                                                             |

| 16                    | $\overline{CS}$ : Chip Select. When this pin is at $V_{DD}$ , the chip is disabled and the data outputs D0 - D3 and Data Change output go open circuit. When at $V_{ss}$ the chip is enabled and the IRQ output is reset to logic "1."                                                                                                                                                                                                                |

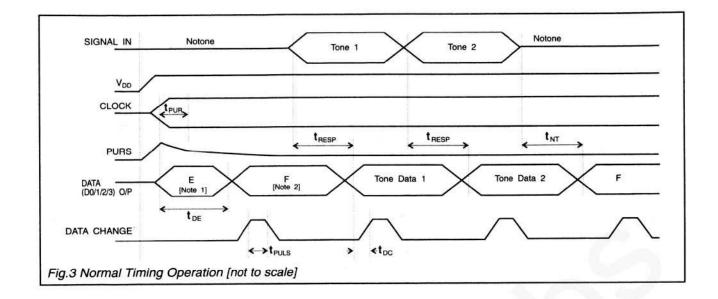

| 17                    | <b>Data Change:</b> A 1.0 ms pulse is generated at this pin upon detection of a valid tone and new data is presented to the D0 - D3 outputs. The signal from this pin can be latched at a logic "1" after detection of a tone (see Hold input). This output is tri-state.                                                                                                                                                                             |

| 19<br>20<br>22<br>23  | D3Data Outputs:A 4-bit word, that represents the HEX value of the decoded tone<br>frequency, is output from these pins after a successful decode.D1These outputs are tri-state. See Table 1.D0                                                                                                                                                                                                                                                        |

| 24                    | V <sub>pp</sub> : Positive Supply                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1, 2, 4, 6,<br>18, 21 | Not connected. Leave open-circuit.                                                                                                                                                                                                                                                                                                                                                                                                                    |

## **Application Information**

#### **Timing Specification**

|                   | Min. | Тур. | Max. | Unit |

|-------------------|------|------|------|------|

| t <sub>PUR</sub>  | 2.0  | -    | -    | ms   |

| t <sub>DE</sub>   | -    | 33.0 | -    | ms   |

| t <sub>PULS</sub> |      | 1.0  | -    | ms   |

| t <sub>DC</sub>   | 0.5  | -    | 1.0  | ms   |

| t <sub>RESP</sub> | 20.0 | -    | 33.0 | ms   |

| t <sub>NT</sub>   | 33.0 | -    | 53.0 | ms   |

| t <sub>DATA</sub> |      | -    | 2.0  | ms   |

|                   | -    | -    | 120  | μs   |

| t <sub>HOLD</sub> | 50.0 | -    | -    | μs   |

| t <sub>iRQ</sub>  | -    |      | 250  | ns   |

| t <sub>RIRQ</sub> | 20.5 |      | 34.0 | ms   |

| tACS              | -    | -    | 250  | ns   |

| t <sub>ohr</sub>  | -    | -    | 100  | ns   |

#### Notes:

- 1. 'E' is the start-up (power-up reset) condition.

- The state of D0/1/2/3 will represent the input frequency present during and after Power-Up Reset (F [NOTONE] in the Figure 3 example).

#### Specification

#### **Absolute Maximum Ratings**

Exceeding the maximum rating can result in device damage. Operation of the device outside the operating limits is not implied.

| Functional Limits                                              | Min. Max. Unit                   |  |  |  |  |

|----------------------------------------------------------------|----------------------------------|--|--|--|--|

| Storage temperature range (T <sub>ST</sub> ): <b>FX013J/LG</b> | -55°C to +125°C                  |  |  |  |  |

| Operating Temperature (T <sub>OP</sub> ): <b>FX013J/LG</b>     | -40°C to +85°C                   |  |  |  |  |

| Derating                                                       | 10mW/°C                          |  |  |  |  |

| Total device dissipation @ T <sub>AMB</sub> 25°C               | 800mW Max.                       |  |  |  |  |

| (other pins)                                                   | +/- 20mA                         |  |  |  |  |

| Sink/source current (supply pins)                              | +/- 30mA                         |  |  |  |  |

| Input voltage at any pin (ref $V_{ss} = 0V$ )                  | -0.3 to (V <sub>DD</sub> + 0.3V) |  |  |  |  |

| Supply voltage                                                 | -0.3 to 7.0V                     |  |  |  |  |

|                                                                |                                  |  |  |  |  |

Supply Voltage (V<sub>DD</sub>)

2.5 5.5 V at 25°C

All device characteristics are measured under the following conditions unless otherwise specified:

V<sub>DD</sub> = 5.0V T<sub>OP</sub> = -40 to +85 °C. Xtal/Clock or 'Clock In' Frequency = 560kHz.

| Characteristics                         | See Note   | Min.  | Тур.            | Max.               | Unit  |

|-----------------------------------------|------------|-------|-----------------|--------------------|-------|

| Static Values                           |            |       |                 |                    |       |

| Supply Voltage (V <sub>ss</sub> =0V)    |            | 2.5   | -               | 5.5                | V     |

| Supply Current                          |            | )#    | 500             | -                  | μÂ    |

| Logic "1" Output (Source = 1 mA)        | 1          | 4.5   |                 | -                  | v     |

| Logic "0" Output (Sink = 1 mA)          | 1          | -     | -               | 0.5                | v     |

| Logic "1" Input Level                   | 2          | 3.5   |                 | -                  | v     |

| Logic "0" Input Level                   | 2          | 12    | <u>4</u>        | 1.5                | v     |

| Oscillator Output Level                 |            |       |                 |                    |       |

| Input Impedances                        |            |       |                 |                    |       |

| Signal In                               |            |       | 1.0             | -                  | MΩ    |

| Clock Select                            |            |       | 1.0             | 2                  | MΩ    |

| Hold I/P                                |            | -     | 1.0             | -                  | MΩ    |

| Chip Select                             |            | -     | 10.0            | -                  | MΩ    |

| Output Impedances                       |            |       |                 |                    |       |

| D0 - D3                                 |            |       | 1.0             | -                  | kΩ    |

| Data Change                             |            | -     | 1.0             | -                  | kΩ    |

| Oscillator Outputs                      |            | 2     | 10.0            | -                  | kΩ    |

| Dynamic Values                          |            |       | 0.2-017-01.2000 |                    |       |

| Signal Input Range                      | 3          | 35.0  | -               | V <sub>pp</sub> /2 | mVrms |

| Decode Bandwidth when P>0.995           |            |       |                 | - 00               |       |

| QA                                      | 4          | ±20.0 | -               | -                  | Hz    |

| QC                                      | 4          | ±1.0  | 0.000           | -                  | %     |

| Not-Decode Bandwidth when P<0.03        |            |       |                 |                    |       |

| QA                                      | 5          | -     | -               | ±60.0              | Hz    |

| QC                                      | 5          | -     | -               | ±3.0               | %     |

| Noise Response Rate (hours per F - F    | - F single |       |                 |                    |       |

| character response with no input tone). |            |       |                 |                    |       |

| QA                                      | 6          | -     | 0.15            | -                  | /hour |

| QC                                      | 6          | -     | 40.0            | -                  | /hour |

| Decode Response Time:                   |            |       | 122212/2022     |                    |       |

| NOTONE to Tone (F - F)                  | 7          | 20.0  | 25.0            | 33.0               | ms    |

| Tone to NOTONE, Tf (F - F)              | 7          | 33.0  | -               | 53.0               | ms    |

| Minimum inter-tone gap for "F"          | 8          | 15.0  | -               | 28.0               | ms    |

#### Notes:

1. Pins 7, 8, 17 and 19, 20, 22 and 23.

2. Pins 13,14 and 16.

3. An ac coupled sine/squarewave.

4. With minimum tone period (Tp) specified for toneset. P = Decode Probability. (QA) SNR = 3dB. (QC) SNR = 0dB.

5. All conditions of input SNR and amplitude with maximum Tp specified for the toneset.

Gaussian input noise, bandwidth 6.0kHz, maximum input level corresponds to 1-digit code falsing rate. F = random single character.

7. Delay from change of input (tone applied/removed) to change at Q0-Q3 outputs.

8. Included in t<sub>NT</sub>. Minimum tone gap requirement for "NOTONE" recognition. Outputs = F after delay.

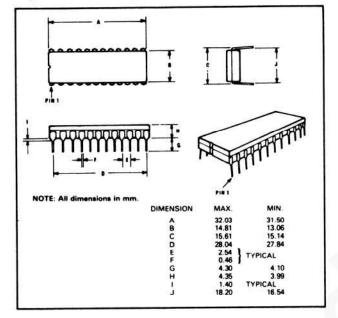

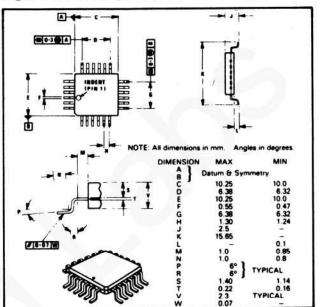

### **Package Outlines**

The FX013J, the cerdip package is shown in Figure 6 and the 'LG' quad plastic version in Figure 7.

Pin 1 identification marking is shown on the relevant diagram and pins on both package styles number anti-clockwise when viewed from the top (marked side).

#### Fig.6 FX013J 24-pin cerdip Package

#### **Handling Precautions**

The FX013 is a CMOS LSI circuit which includes input protection. However precautions should be taken to prevent static discharges which may cause damage.

#### Fig.7 FX013LG quad plastic Package

## **Ordering Information**

The FX013 is available in two tonesets and two package styles: 'A' = EIA Tones 'C' = CCIR Tones Please order the correct toneset in the correct package.

FX013J 'A' / 'C'

24-pin cerdip DIL

FX013LG 'A' / 'C'

24-pin plastic encapsulated bent and cropped

CML does not assume any responsibility for the use of any circuitry described. No circuit patent licences are implied and CML reserves the right at any time without notice to change the said circuitry.