# CML Semiconductor Products

## FX105 Tone Detector

Publication D/105/3/12/0

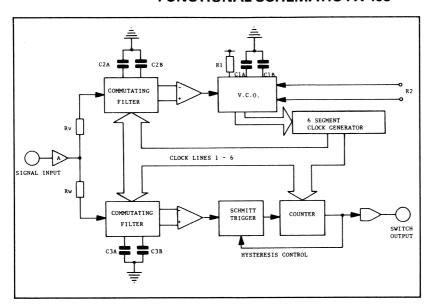

### **FUNCTIONAL SCHEMATIC FX-105**

## FX 105 TONE DETECTOR

https://islandlabs.eu

### **FEATURES**

- OPERATES IN HIGH NOISE CONDITIONS

- >40dB SIGNAL INPUT RANGE

- SIMULTANEOUS TONE DETECTION

- ADJUSTABLE BANDWIDTH

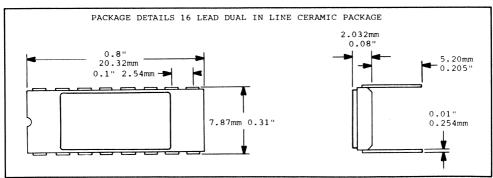

- HERMETICALLY SEALED CERAMIC PACKAGE

- WIDE FREQUENCY RANGE

### **DESCRIPTION**

The FX-105 is a monolithic tone operated switch, designed for tone decoding in single and multitone signalling systems.

The device employs decoding techniques which allow tones to be recognised in the presence of high noise levels or strong adjacent channel tones.

Tone channel centre frequency and channel bandwidth can each be adjusted independently. The circuit has a high noise immunity against harmonic and sub-harmonic responses and is able to maintain a constant bandwidth and high noise immunity over a wide range of input signal levels.

#### METHOD OF OPERATION

Input signals are A.C. coupled to the buffer input, which is internally biased at 50% of supply voltage, the signal appears at the output of the buffer as an A.C. voltage superimposed on the D.C. bias level. The signal is then coupled via RV and RW to the voltage controlled oscillator and word sampling switches, which sequentially connect C2 and C3 into circuit to form four sample and hold RC integrators.

With no input signal, each capacitor charges to the D.C. bias level and differential voltages are zero. When an input signal is applied, each capacitor receives an additional charge according to the integrated average of the signal waveform during the interval the capacitor is switched into circuit.

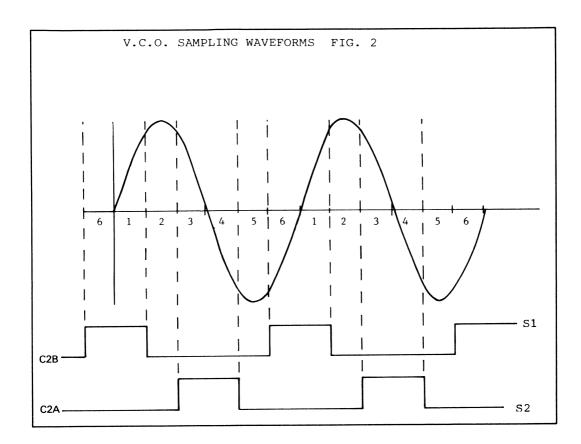

Figure 2 above shows the operating sequence of the V.C.O. sampling switches and their phase relationship to a locked on inband signal. As can be seen from Figure 2 C2A and C2B should not receive any additional charge as they always sample the input as it crosses the D.C. bias level. Should the signal not be locked to the V.C.O. then a positive or negative charge voltage will appear on C2A or

C2B, this voltage when differentially amplified is applied to the V.C.O. as an error correcting signal to enable the V.C.O. to achieve lock.

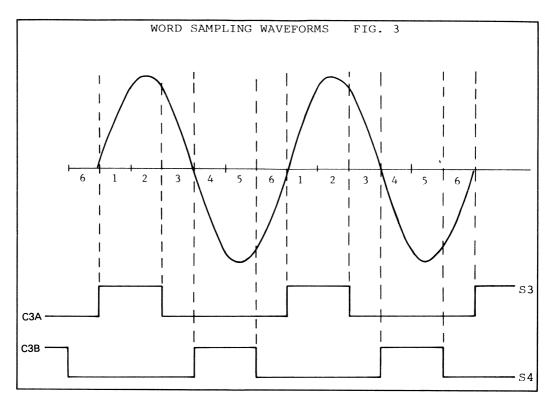

Figure 3 shows the operating sequence of the 'Word' sampling switches and their relationship to a locked on inband signal. As can be seen from Figure 3 the charge being applied to C3A should always be positive and the charge applied to C3B should always be negative with respect to the common bias level.

These capacitor potentials are differentially amplified and applied to a D.C. comparator, which switches at a predetermined threshold voltage. The comparator output is a logic signal used to control a counter which switches the FX-105 output ON when the comparator output is maintained in the 'Word Present' state for a minimum number of consecutive signal samples. The output switch reduces the comparator threshold by 50% when turned on, thereby introducing threshold hysterises which minimises output chatter with marginal input signal amplitudes.

### METHOD FOR CALCULATING EXTERNAL COMPONENT VALUES

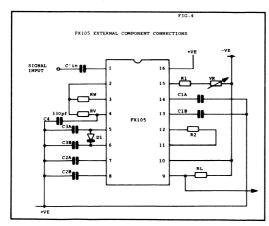

The external components shown below in Figure 4 are used to adjust the various performance parameters of the FX-105. The signal to noise performance, turn on delay and signal bandwidth are all interrelated factors which should be optimised to meet the requirements of the application.

By selecting component values in accordance with the following graphs nominally optimum circuit performance is obtained for any given application.

The user should first define the following application parameters.

- A. The centre frequency to be detected (f'o).

- B. The FX-105 Minimum Usable Bandwidth (MUBW). This is obtained by taking into account the worst case tolerances on the input tone frequency and variations in the FX-105 f'o due to supply voltage (0.07%/%) and ambient temperature (0.02%/°C) changes.

- C. The maximum permissible FX-105 response time.

- D. The minimum input signal amplitude.

Using this information the appropriate component values can be calculated, and the signal to noise performance obtained may then be read from a chart.

Using the graphs overleaf the following worked example may be used to calculate component values for any given application.

- A. FX-105 centre band frequency (f'o) = 2800Hz.

- B. FX-105 bandwidth = 6%.

- C. FX-105 maximum response time = 50ms.

- D. Minimum input signal amplitude = 200 mVolts R.M.S.

#### **R1 C1A C1B**

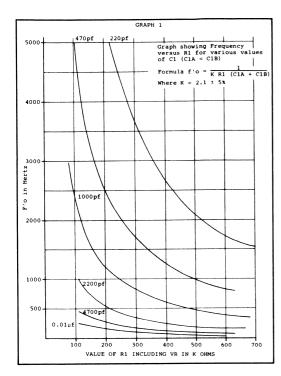

These components set the free running frequency of the V.C.O. and thereby the centre band frequency of the FX-105.

By using graph number 1 the frequency 2800Hz can be seen to correspond to a value of capacitor of 220 picofarads and a resistor value of 385k ohms, this resistance can be achieved with a 300k ohm fixed resistor for R1 and a 100k ohm potentiometer.

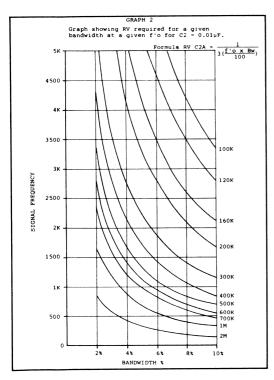

Graph number 2 shows that for a frequency of 2800Hz and a bandwidth of 6% a resistor RV of 200k ohms and a capacitance for C2A and C2B of 0.01 microfarads will be required.

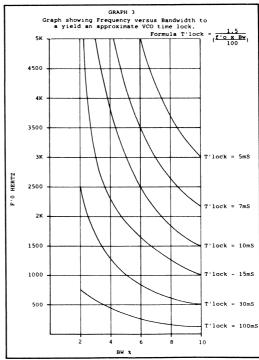

The response time of the FX-105 is the sum of the V.C.O. 'Lock' time (T'lock) and the 'Word' integration time (T'word).

Graph number 3 shows that for a frequency of 2800Hz and a bandwidth of 6% the approximate 'Lock' time will be 9 milliseconds, as we have a maximum response time of 50 milliseconds, this allows for a 'Word' time of 41 milliseconds.

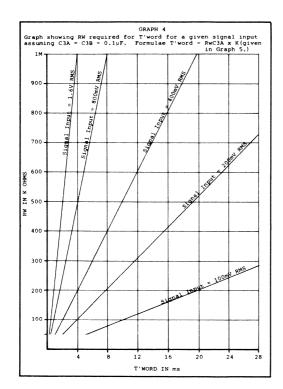

Graph number 4 shows that for a signal amplitude of 200 mVolts, a resistor value RW of 510 k ohms with a 0.1 microfarad capacitor for C3A and B will yield a 'Word' time of 20 ms. This will yield a response time of 9 ms + 20 ms = 29 ms.

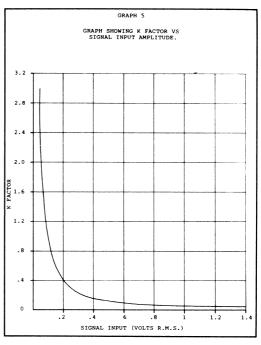

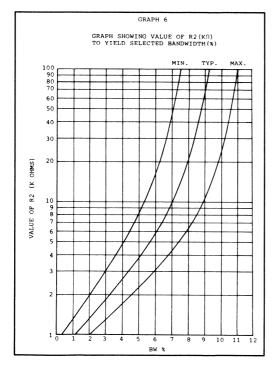

Graph 6 shows the range of values for R2 to yield a given bandwidth. The exact bandwidth given by any value of R2 will vary with differing production batches, therefore in applications where an exact bandwidth is required R2 should be a variable resistor which is adjusted on test.

To calculate the worst case signal to noise ratio the FX-105 will work with the above component values. The formula is as follows:

$$M = \frac{f'o \times Bw}{100} \times (Rw C3A)$$

∴ M =  $\frac{2800 \times 6}{100} \times (0.51MΩ \times 0.1μF)$

∴ M =  $168 \times 0.051$

∴ M ≈  $8.57$

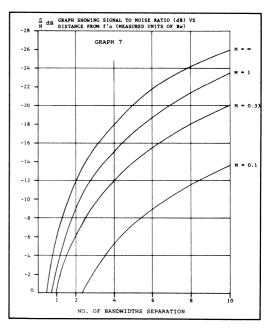

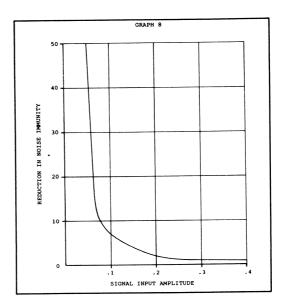

By substituting the value for M of 8.57 in graph number 7 the signal to noise ratio of an adjacent tone can be found, this then has to be decreased depending upon the tone amplitude. The figure to decrease SNR by is given in graph 8.

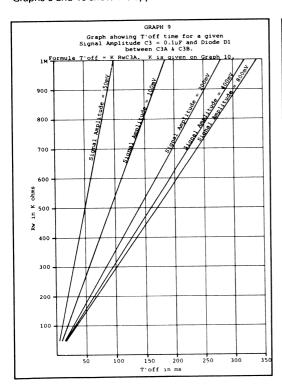

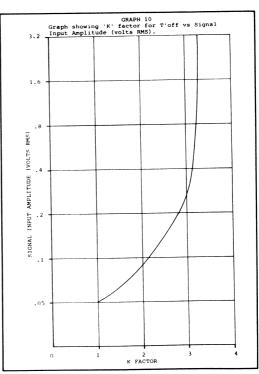

Graphs 9 and 10 show the approximate time the FX-105

will take to turn off after an inband signal has been removed. The turn off time is calculated with a diode (1N914 or similar) between pins 5 and 6 as shown in Figure 4. The effect of this diode is to greatly reduce the turn off time with signal input amplitudes greater than 300mV R.M.S.

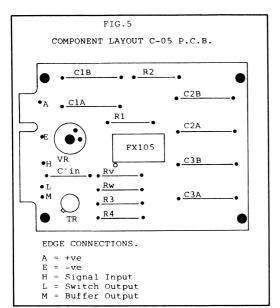

To assist engineers in designing systems utilising the FX-105, C.M.L. have produced a printed circuit board, allowing the necessary external components to be connected, so that a full working system may be easily and quickly constructed. Please note there is no provision on the P.C.B. for capacitor C4 or diode D1 and it is recommended that these components are added for improved system operation.

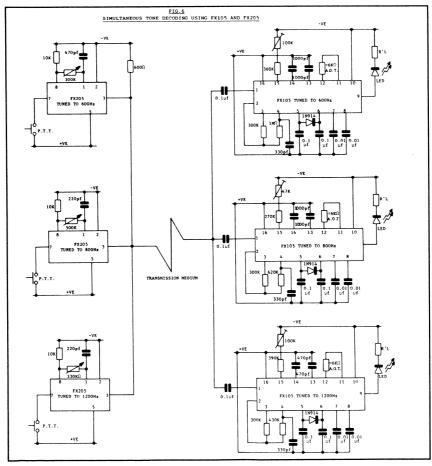

Due to the FX-105's ability to decode tones in the presence of adjacent channel tones or noise, the device is ideally suited to applications where a number of tones are sequentially or simultaneously transmitted over a common link. In the example shown in Figure 6 a number of single tone transmitters (FX-205) are transmitting over a common link such as cable, radio, optical, etc., to a number of receivers (FX-105). The transmitters may transmit either individually or simultaneously to the FX-105s without the possibility of missing a call or receiving a false call.

### **SPECIFICATION**

### MAX. RATINGS Failure to observe may result in device damage.

| MAX. VOLTAGE BETWEEN ANY PIN AND + VE SUPPLY (pin 16) | 20V  and  + 0.3V                    |

|-------------------------------------------------------|-------------------------------------|

| OPERATING TEMPERATURE RANGE                           | 30°C to +85°C                       |

| STORAGE TEMPERATURE RANGE                             | $-55^{\circ}$ C to $+125^{\circ}$ C |

| DEVICE DISSIPATION (at 20°C ambient temperature)      | 400mW                               |

| MAX. OUTPUT SWITCH LOAD CURRENT                       | 10mA                                |

### **CHARACTERISTICS**

Note: Due to A.C. signal coupling either supply polarity may be 'ground'.

| SYMBOL         | PARAMETER                  | NOTES                         | MIN.  | TYP.     | MAX.           | UNITS           |

|----------------|----------------------------|-------------------------------|-------|----------|----------------|-----------------|

| V <sub>s</sub> | Supply voltage             | Operating range               | 10    | 12       | 15             | Volts           |

| l <sub>s</sub> | Supply current             | Total, excluding loads        |       | 5        |                | mA              |

|                | Signal Input               | Signal + noise range          | 0.055 |          | 5 <sup>1</sup> | Volts<br>R.M.S. |

| F'o            | Channel<br>Frequency       |                               | 0.04  |          | 5              | kHz             |

| Bw             | Bandwidth                  |                               | 2%    |          | 10%            |                 |

|                | O/P switch<br>load current |                               |       | -        | 10             | mA              |

| Zin            | Input impedance            |                               |       | 200      | -              | k ohm           |

|                | Frequency<br>Stability     | vs T'AMB                      |       | 0.02%/°C | :              |                 |

|                | Frequency<br>Stability     | Per 1% change in supply volts |       | 0.07%    |                |                 |

#### NOTE

For input voltages greater than VDD x 0.143 pins 1 and 2 should be open circuit and the signal applied via C'in to the junction of RV and RW.

CML DOES NOT ASSUME ANY RESPONSIBILITY FOR THE USE OF ANY CIRCUITRY DESCRIBED. NO CIRCUIT PATENT LICENCES ARE IMPLIED AND CML RESERVES THE RIGHT AT ANY TIME WITHOUT NOTICE TO CHANGE SAID CIRCUITRY.