# **Consumer Microcircuits Limited**

PRODUCT INFORMATION

FX406 Unifil<sup>™</sup> Universal Analogue Signal Process

With compliments of Island Labs

Publication D/406/5 September 1986 Provisional Issue

#### **Features**

- 2nd Order Multiple Filter

- **PLL Clock Generator**

- Programmable Q

- F<sub>c</sub> set by RC or External Clock

- Gain Adjustment on Inputs

- Single 5 Volt Supply CMOS

## **Applications**

- Programmable Filters

- Voltage Controlled Filters

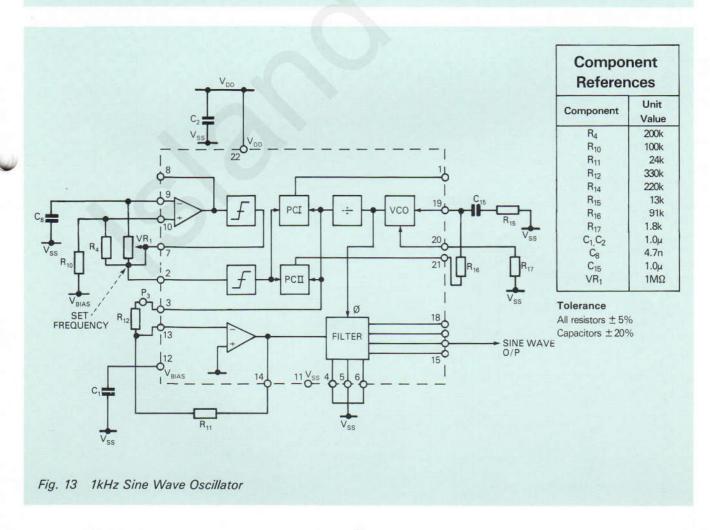

- Sinewave Oscillator

- Tracking Filters/Oscillators

- FSK and PSK Modems

- Square-Sine, Pulse-Sine Converter

**FX406**

## **Brief Description**

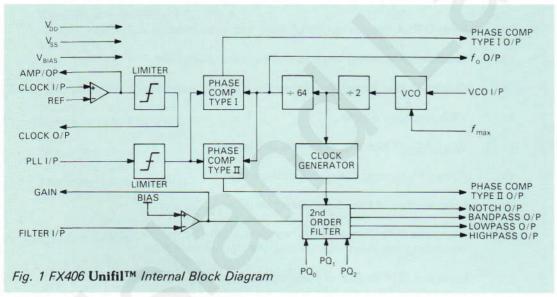

The FX406 Unifil™ is a CMOS LSI circuit with a wide variety of signal processing applications. The device consists of a switched capacitor second order active filter with a single input and outputs for bandpass, notch, lowpass and highpass frequency responses, together with a clock generator to provide the switched capacitor sampling clock frequency. The centre frequency of the bandpass and notch filters is the same as the cut-off frequency foof the lowpass and highpass filters. The filter sampling clock is

derived from a multiplying phase locked loop whose reference or input frequency is the same as the desired cut-off frequency of the filters. The PLL comprises a voltage controlled oscillator, one of two types of phase comparator, a fixed divider and an external RC loop filter. Facilities are provided to programme the cut-off frequency of the filters by injecting an external signal into the PLL, or by using the on-chip clock oscillator circuit. The filters have gain adjustment on the input and the Q is programmable to eight values between 0.54 and 8.0.

| FX406J      | FX406LG     | FX406LH                      |                                                                                                                                                                                                                          |  |  |  |

|-------------|-------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1           | 1           | 3                            | PCI O/P: Output of 'EXCLUSIVE-OR' type phase comparator. See Note on PLL operation.                                                                                                                                      |  |  |  |

| 2           | 2           | 4                            | PLL I/P: Input to limiter preceding phase comparators.                                                                                                                                                                   |  |  |  |

| 3           | 4           | 5                            | $f_{o}$ O/P: Divided down VCO square wave output.                                                                                                                                                                        |  |  |  |

| 4<br>5<br>6 | 5<br>6<br>7 | 6<br>7<br>8                  | $PQ_0$ PQ $I/P$ : These pins set the Q of the filters; they have internal resistors to set Q = 0.71 if left open circuit (logic state 101, $\approx$ 1M $\Omega$ ). Possible Q values are:                               |  |  |  |

|             |             |                              | PQ <sub>2</sub> PQ <sub>1</sub> PQ <sub>0</sub> Q 1 1 1 1 0.54* 1 0 0.58 (Bessel) 1 0 1 0.71 (Butterworth) 1 0 0 1.00 0 1 1 1.31 0 1 0 2.00 0 0 1 4.00 0 0 0 8.00                                                        |  |  |  |

| 7           | 8           | 9                            | *(Cascaded with a 1.31 section for a 4th order Butterworth filter).  Clock O/P: Digital output of clock oscillator circuit.                                                                                              |  |  |  |

| 8           | 10          | 10                           | Amp O/P: Analogue output of clock oscillator amplifier.                                                                                                                                                                  |  |  |  |

| 9           | 11          | 13                           | Reference: Inverting input to clock oscillator amplifier.                                                                                                                                                                |  |  |  |

| 10          | 12          | 14                           | Clock I/P: Non-inverting input to clock oscillator amplifier.                                                                                                                                                            |  |  |  |

| 11          | 13          | 15                           | VSS: Negative supply.                                                                                                                                                                                                    |  |  |  |

| 12          | 14          | 16                           | V <sub>BIAS</sub> : V <sub>DD</sub> /2 bias pin, externally decoupled.                                                                                                                                                   |  |  |  |

| 13          | 15          | 17                           | Filter I/P: Input to filter input buffer amplifier.                                                                                                                                                                      |  |  |  |

| 14          | 16          | 19                           | Gain: Output of filter input buffer amplifier.                                                                                                                                                                           |  |  |  |

| 15          | 17          | 21                           | Highpass O/P: Output of the highpass filter. The cut-off frequency is identical to the input frequency to the PLL when locked.                                                                                           |  |  |  |

| 16          | 18          | 22                           | Lowpass O/P: Output of the lowpass filter. The cutoff frequency is the same as the highpass filter.                                                                                                                      |  |  |  |

| 17          | 19          | 23                           | <b>Bandpass O/P:</b> Output of the bandpass filter. $f_0$ is indentical to the input frequency to the PLL when locked. Gain in passband is dependent on Q.                                                               |  |  |  |

| 18          | 20          | 24                           | Notch $O/P$ : Output of the notch filter, $f_o$ , is the same as the bandpass filter.                                                                                                                                    |  |  |  |

| 19          | 21          | 26                           | VCO I/P: Input of the VCO control voltage, usually connected to loop filter output.                                                                                                                                      |  |  |  |

| 20          | 22          | 28                           | $f_{\text{max}}$ : This pin is connected to V <sub>SS</sub> via an external resistor R <sub>max</sub> (R <sub>17</sub> , see Fig. 7). The value sets the maximum frequency of operation of the VCO, See Fig. 9(a) & (b). |  |  |  |

| 21          | 23          | 1                            | <b>PCI O/P:</b> Output of the edge-triggered type of phase comparator. See Note on PLL operation.                                                                                                                        |  |  |  |

| 22          | 24          | 2                            | V <sub>DD</sub> : Positive supply.                                                                                                                                                                                       |  |  |  |

| -           | 3, 9        | 11, 12,<br>18, 20,<br>27, 27 | No Connection: Leave open circuit.                                                                                                                                                                                       |  |  |  |

## **Specification**

#### **Absolute Maximum Ratings**

Exceeding the maximum rating can result in device damage. Operation of the device outside the operating limits is not implied.

| Supply voltage                                | -0.3V to 7.0V |                                     |  |

|-----------------------------------------------|---------------|-------------------------------------|--|

| Input voltage at any pin (ref $V_{SS} = OV$ ) |               | $-0.3V$ to $(V_{DD} + 0.3V)$        |  |

| Output sink/source current (total             |               | 20mA                                |  |

| Operating temperature range: F                |               | $-30^{\circ}$ C to $+85^{\circ}$ C  |  |

|                                               | X406LG/LH     | $-30^{\circ}$ C to $+70^{\circ}$ C  |  |

| Storage temperature range: F                  | X406J         | $-55^{\circ}$ C to $+125^{\circ}$ C |  |

|                                               | X406LG/LH     | $-40^{\circ}$ C to $+85^{\circ}$ C  |  |

| Maximum device dissipation:                   |               | All versions 100mW                  |  |

#### **Operating Limits**

Typical characteristics measured using the following parameters unless otherwise specified:

$V_{DD} = 5V$ ,  $T_{amb} = 25^{\circ}C$ , PLL input = 1kHz, filter Q = 0.707.

Limits specified over the full operating temperature and working voltage range.

| Characteristics                                                        | See Note | Min                 | Тур                  | Max                 | Unit      |

|------------------------------------------------------------------------|----------|---------------------|----------------------|---------------------|-----------|

| Static Characteristics                                                 |          |                     |                      |                     |           |

| Supply voltage                                                         |          | 4.5                 | 5.0                  | 5.5                 | ٧.        |

| Supply current                                                         |          | _                   | 4.5                  | 8.5                 | mA        |

| Input impedance (Filter & Clock Osc)                                   |          | 1.0                 |                      |                     | $M\Omega$ |

| Output impedance (Filter Outputs)                                      |          | _                   | -                    | 1.0                 | $k\Omega$ |

| Output impedance (Clock Output)                                        |          |                     |                      | 1.0                 | kΩ        |

| Input impedance (PQ <sub>0</sub> , PQ <sub>1</sub> , PQ <sub>2</sub> ) |          | 250                 |                      | _                   | kΩ        |

| Output impedance (fo output)                                           |          | _                   | 200                  | 5.0                 | kΩ        |

| Input logic '1'                                                        |          | 70% V <sub>DD</sub> | A -                  | -                   | V         |

| Input logic '0'                                                        |          | -                   | 4 -                  | 30% V <sub>DD</sub> | V         |

| Filter Characteristics                                                 |          |                     |                      |                     |           |

| Maximum cutoff frequency                                               |          | 4.0                 | 5.0                  | -                   | kHz       |

| Minimum cutoff frequency                                               |          | _                   | 50                   | 100                 | Hz        |

| Gain at f <sub>c</sub> (f <sub>o</sub> ) (HP BP LP)                    |          | _                   | 20 log Q             | _                   | dB        |

| Notch filter depth                                                     | 1        | _                   | -30                  | -                   | dB        |

| Notch accuracy                                                         | 1        | _                   | ±0.5% f <sub>o</sub> | _                   | Hz        |

| Maximum signal handling                                                | 1 2      | 3.0                 | _                    | _                   | Vp-p      |

| No signal filter noise (BP)                                            |          | _                   | 6.0                  | _                   | mVrms     |

| (LP HP N)                                                              |          | _                   | 3.0                  | _                   | mVrms     |

| VCO Characteristics                                                    |          |                     |                      |                     |           |

| VCO maximum frequency                                                  | 3        | 4.0                 | 5.0                  | _                   | kHz       |

| VCO minimum frequency                                                  | 3        | _                   | 50                   | 100                 | Hz        |

| VCO input impedance                                                    |          | 1.0                 | _                    |                     | $M\Omega$ |

| Phase Comparator Characteristics                                       |          |                     |                      |                     |           |

| Input impedance                                                        |          | 100                 | 500                  | _                   | kΩ        |

| Input sensitivity                                                      | 4        | 30                  | 10                   | _                   | mVrms     |

| Output impedance PCII                                                  | 5        | _                   | _                    | 1.5                 | kΩ        |

| PCI                                                                    |          | -                   | _                    | 1.5                 | $k\Omega$ |

| Amplifier Characteristics (Clock Oscillator and Filter inputs)         |          |                     |                      |                     |           |

| Open loop gain                                                         |          | 40                  |                      | _                   | dB        |

| Input offset voltage                                                   |          | _                   | _                    | 10                  | mV        |

| Maximum signal handling                                                | 2        | 3.0                 | -                    | -                   | Vp-p      |

|                                                                        |          |                     |                      |                     |           |

Notes: 1. Q = 8.

2. For SINAD = 30dB at output.

3. VCO frequency divided down at fo output.

4. At PLL input pin, ac coupled.

5. Output impedance when conducting, output is high impedance three-state when PLL is in lock.

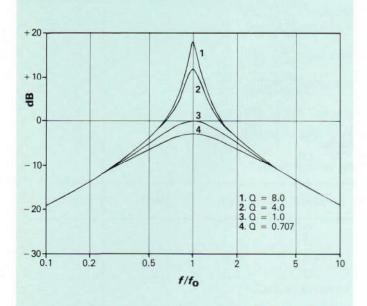

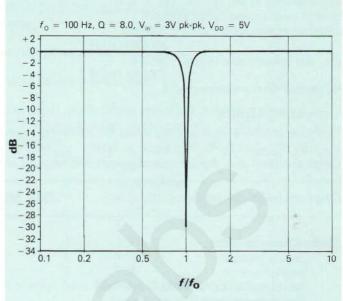

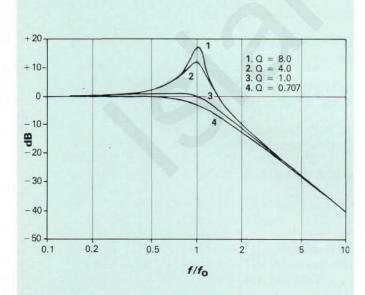

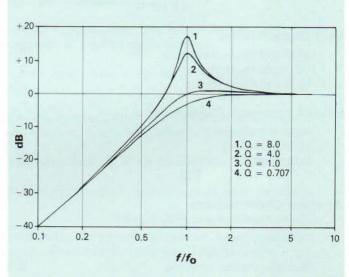

## **Typical Filter Frequency Responses**

Fig. 2 Bandpass Frequency Response for different Q Values

Fig. 3 Notch Frequency Response

Fig. 4 Lowpass Frequency Response for different Q Values

Fig. 5 Highpass Frequency Response for different Q Values

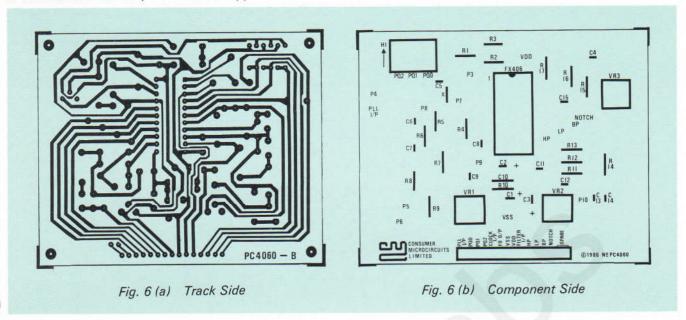

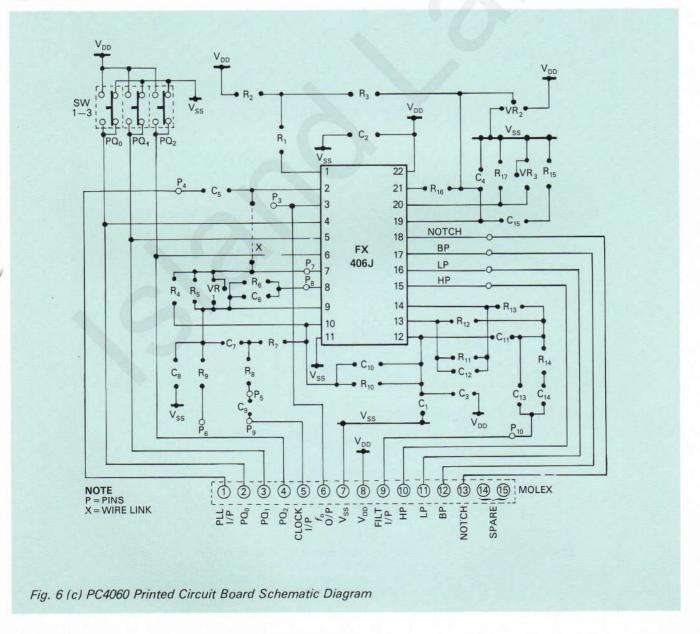

## **PC4060 PCB For Design Evaluation**

To assist in customer's design evaluation of the FX406, a PCB is available to enable external components to be connected for easy evaluation of application circuits.

Fig. 6 PC4060 Printed Circuit Board

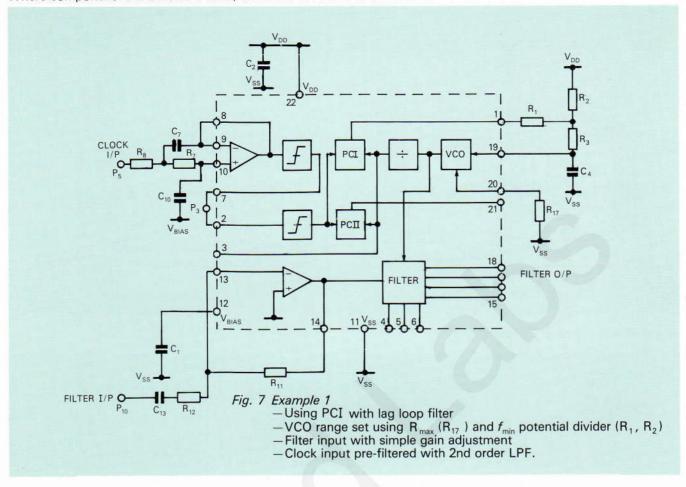

#### **External Component Connections**

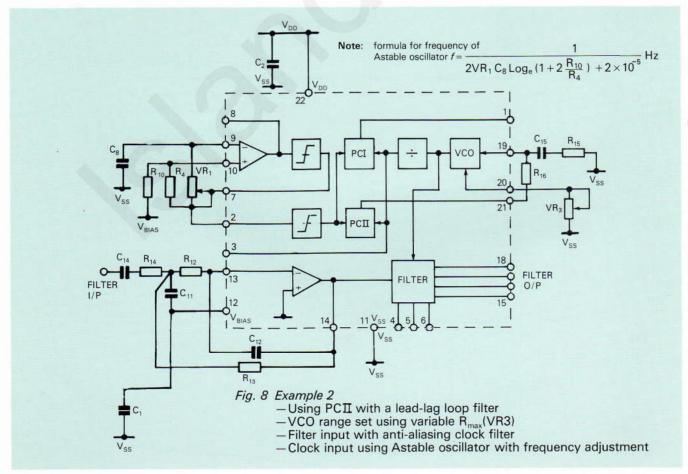

The following examples of external component connections illustrate the basic modes of operation of the FX406. Where component references are used, these are the same as the circuit references on the PC4060 Evaluation PCB.

## **Application Notes**

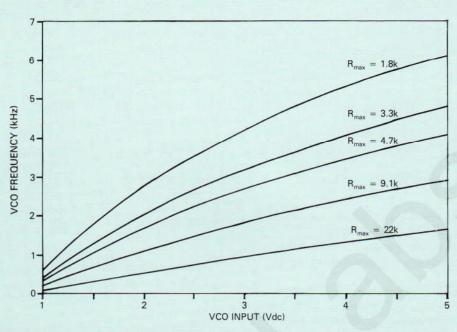

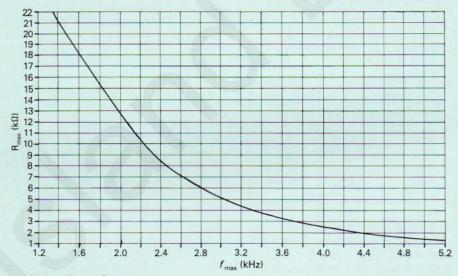

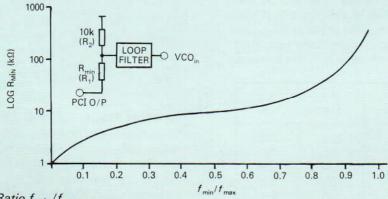

## Note 1 — Setting VCO Frequency Range.

Set  $f_{\text{max}}^*$  of VCO by selecting  $R_{\text{max}}$  using graph in Fig. 9(a) & 9(b). If Phase comparator I is being used, it is also possible to set  $f_{\text{min}}$  of the VCO by using the network shown in Fig. 9(c).  $R_{\text{min}}$  may be determined using the graph in Fig. 9(c).

\*Frequencies shown in graphs are actually  $f_{VCO}/128$ .

Fig. 9(a) VCO Conversion Gain Curves For Different Values of R<sub>max</sub> (R<sub>17</sub>)

Fig. 9(b) VCO f<sub>max</sub> Versus R<sub>max</sub> Curve

Fig. 9(c) R<sub>min</sub> Versus Ratio f<sub>min</sub>/f<sub>max</sub>

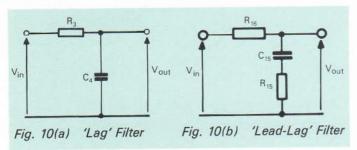

Note 2 - Loop Filter Design

In order to maintain a fixed phase relationship between the VCO and reference input (or clock) signals, a 'second order loop' must be established. This is achieved by placing a lowpass filter between the phase comparator output and the VCO control input

This filter may be a 'lag' filter, (Fig.10a) or for improved stability a 'lead-lag' filter, (Fig10b).

The overall loop gain is given by  $K_p$ .  $K_p \frac{K_{vco.}}{j\omega} K_{div}$

Where: K<sub>p</sub> = phase comparator gain in volts/radian.

$K_F^P$  = filter gain in volts/volt.

K<sub>vco</sub> = VCO conversion gain in radians/sec-volt.

$K_{div}^{vco}$  = divider gain in radians/radian (I/128).

Selection of the frequency at which the loop gain is unity (0dB) depends on the application, the unity gain frequency should be high enough to allow the loop to track expected variations of the reference frequency but low enough to provide a 'flywheel' action to average noise and unwanted input transients.

Some typical loop filter component values for the FX406 using phase comparator  ${\bf I\!I}$  are tabled below.

| Unity gain<br>frequency (Hz) | R <sub>16</sub><br>(Ω) | R <sub>15</sub><br>(Ω) | C <sub>15</sub> (F) |

|------------------------------|------------------------|------------------------|---------------------|

| 50                           | 92k                    | 13k                    | 1μ                  |

| 100                          | 39k                    | 6k2                    | 1μ                  |

| 250                          | 200k                   | 62k                    | 0.1μ                |

| 500                          | 16k                    | 24k                    | 0.1μ                |

When using phase comparator I, the loop filter frequency response may be used to limit the capture range of the loop, that is the range of input frequencies that the loop will lock onto. This property may be used to provide a degree of selectivity if required. The following table shows filter component values for various capture ranges. It should be noted that the loop filter used here is the simple 'lag' filter (i.e.  $R_2=0$ ), this is to minimise ripple at 2 x  $f_{\rm in}$  on the loop filter output which would cause frequency modulation of the switched capacitor filter response.

| Capture Range 2f <sub>c</sub> (Hz) | R <sub>3</sub><br>(Ω) | C₄<br>(F) |

|------------------------------------|-----------------------|-----------|

| 100                                | 470k                  | 340n      |

| 200                                | 100k                  | 390n      |

| 500                                | 100k                  | 68n       |

| 1000                               | 100k                  | 15n       |

| 2000                               | 100k                  | 3.9n      |

### Note 3 — Phase Comparators

The following table shows the principal characteristics of second order loops using phase comparator I ('EXOR') with a 'lag' filter and phase comparator II (edgetriggered) using a 'lead-lag' filter.

| Input duty cycle                                                       | PC I<br>50% optimum                                                | PC II<br>don't care               |

|------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------|

| Locks on harmonics of wanted signal                                    | Yes                                                                | No                                |

| Noise rejection                                                        | Good                                                               | Poor                              |

| Ripple at $2 \times f_{in}$ on loop filter output                      | Yes                                                                | Low                               |

| Lock range, 2f                                                         | $f_{\max} - f_{\min}$                                              | $f_{\rm max} - f_{\rm min}$       |

| Capture range, 2f <sub>c</sub>                                         | $\frac{1}{\tau} \sqrt{\frac{K_p K_{vco} K_{div}}{2^{\tau_1}}} \pi$ | $f_{\text{max}} - f_{\text{min}}$ |

| Frequency of VCO when not in lock                                      | $\frac{f_{\text{max}} - f_{\text{min}}}{2}$                        | $f_{min}$                         |

| Phase angle between $f_{\text{ref}}$ and $f_{\text{vco}}/128$ in lock. | 0° at $f_{\min}$<br>180° at $f_{\max}$<br>90° at mid-point         | 0°                                |

#### Note 4 — Anti-aliasing

The relationship between  $f_{\rm o}$  and the switched capacitor sampling clock in the FX406 is  $f_{\rm clk}=64f_{\rm o}$ . This type of sampled filter produces alias or image responses centred on half the sampling rate, i.e.,  $32f_{\rm o}$ ,

Filters with passbands extending beyond  $32f_0$  will have spurious responses reflected into the passband at a corresponding distance below  $32f_0$ .

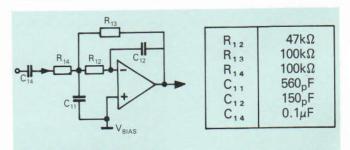

If the input frequency spectrum to the filter is likely to contain components at these alias frequencies then an additional RC filter is required to attenuate these inputs. This is easily accomplished by using the filter input amplifier, Fig. 11 shows a 2nd order 5kHz lowpass filter with passband gain suitable for values of  $f_{\rm o}$  above 250Hz.

Fig. 11 Anti-Aliasing Filter

#### Special Note

Care must be taken when using the FX406 at cut-off below 200Hz as the aliasing frequencies lie within the specified minimum passband of the filter.

On the highpass filter only, an additional lowpass response exists with its  $-3 \mathrm{dB}$  point at  $7 f_\mathrm{c}$  and a roll-off of 20dB/decade.

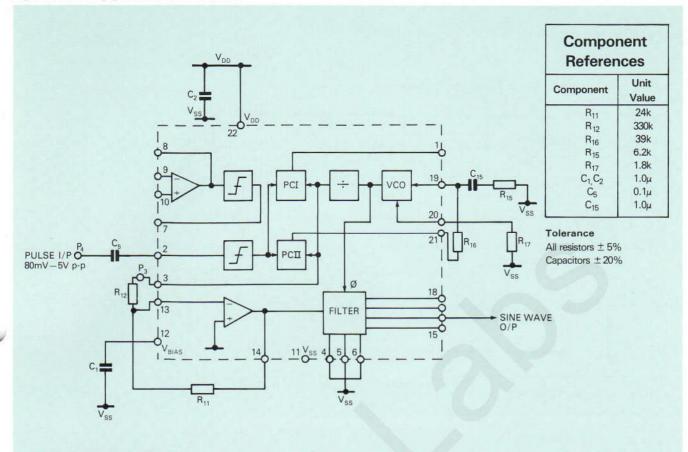

Fig. 12 Pulse to Sine Converter

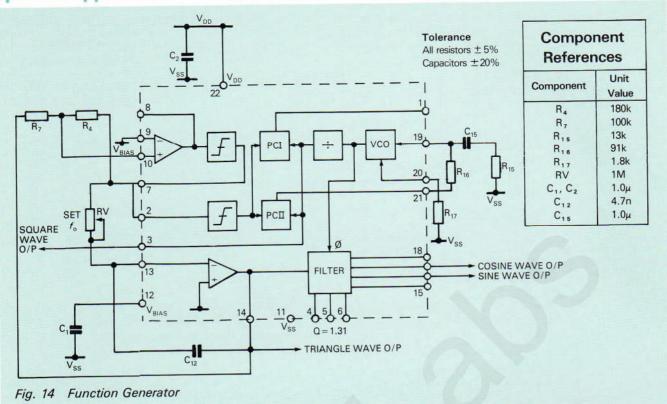

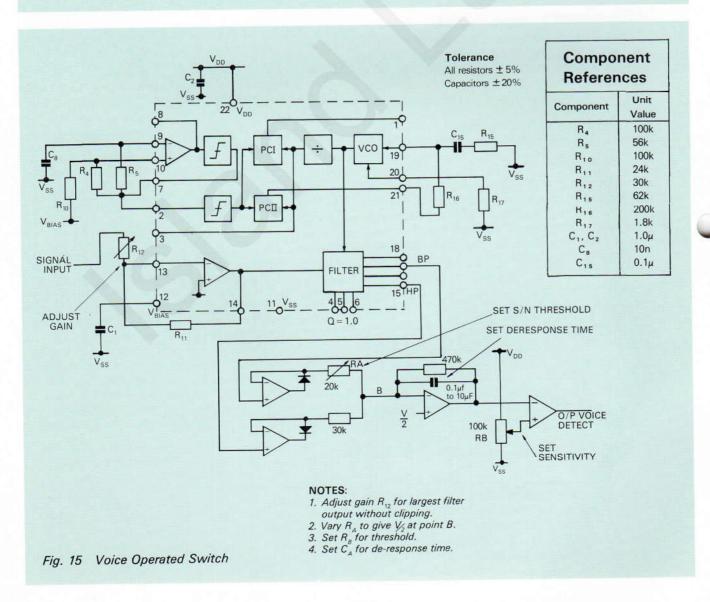

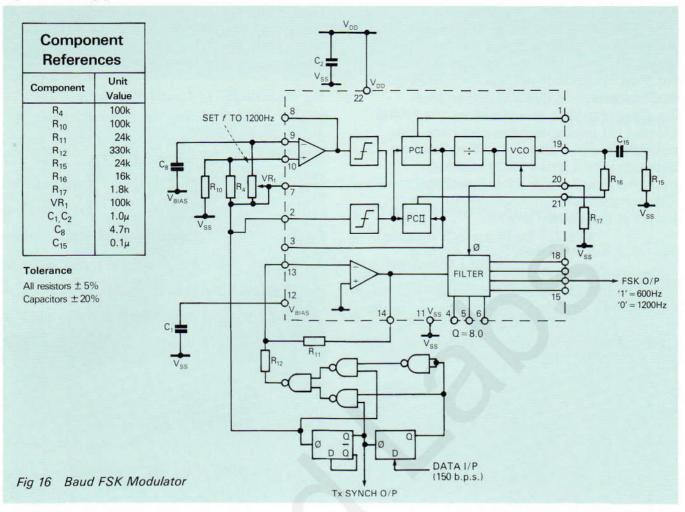

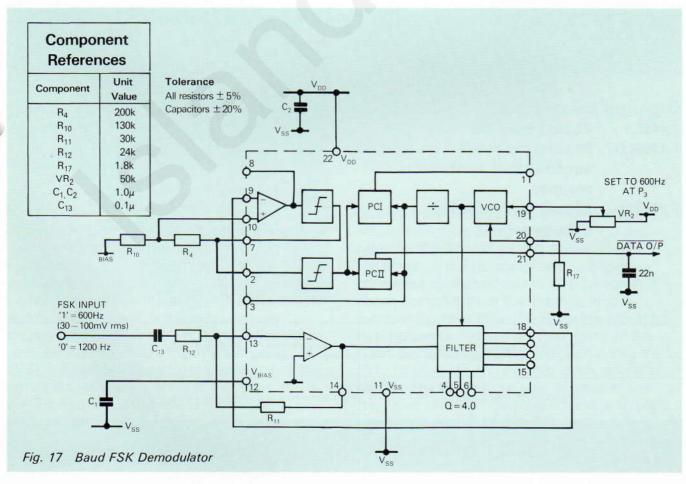

## Specific Application Notes - continued

## Specific Application Notes - continued

#### **Package Outlines**

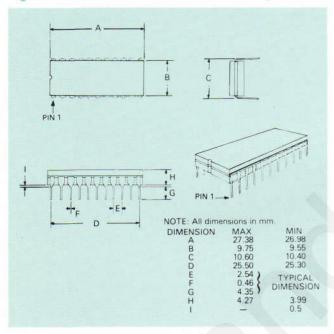

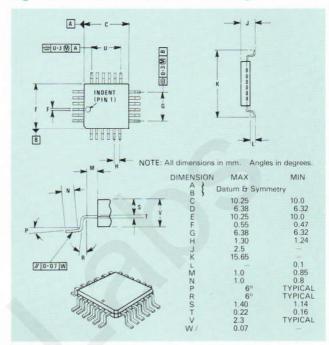

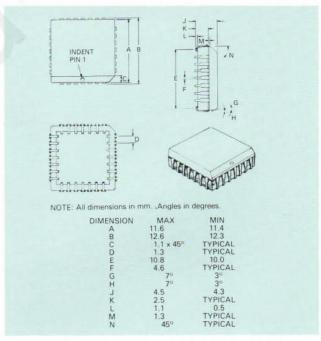

The FX406J, the cerdip package, is illustrated in figure 18. The 'LG' version is shown in figure 19, and the 'LH' version in figure 20. Both 'LG' and 'LH' packages are supplied in conductive trays for handling convenience.

To allow complete identification, the FX406 LG and LH packages have an indent spot adjacent to pin 1 and a chamfered corner between pins 3 and 4 for LG package, between pins 4 and 5 for LH package. Pins number anti-clockwise when viewed from the top (indent side).

Fig. 18 FX406J Unifil™ DIL Package

## Ordering Information

FX406J 22-pin cerdip DIL FX406LG 24-pin quad plastic

encapsulated, bent and

cropped.

FX406LH 28-lead plastic leaded

chip carrier.

#### **Handling Precautions**

The FX406J/LG/LH is a CMOS LSI circuit which includes input protection. However, precautions should be taken to prevent static discharges which may cause damage.

Fig. 19 FX406LG Unifil™ Package

Fig. 20 FX406LH Unifil™ Package

CML does not assume any responsibility for the use of any circuitry described. No circuit patent licences are implied and CML reserves the right at any time without notice to change the said circuitry.

Note: Unifil TM is the distinguishing 'TRADE MARK' (Registration applied for) of the product FX406.

## **CONSUMER MICROCIRCUITS LIMITED**