Features

Algorithm

# **Consumer Microcircuits Limited**

PRODUCT INFORMATION

## **FX609** Continuously Variable Slope Delta Modulation (CVSD) Codec

**On-Chip Input and Output Filters**

Selectable 3 or 4-Bit Compand

Programmable Sampling Clocks

Full Duplex CVSD Codec

Forced Idle Facility

**Powersave Facility**

Low Power 5V CMOS

With compliments of Island Labs Publication D/609/3 March 1988 Provisional Issue

## Applications

- Digital Speech Communications

- Time Domain Scramblers

- Digital Cordless Telephone

- Voice Storage

- Digital Delay Lines

- Speech Analysis

- Multiplexers

- General Purpose

## **Brief Description**

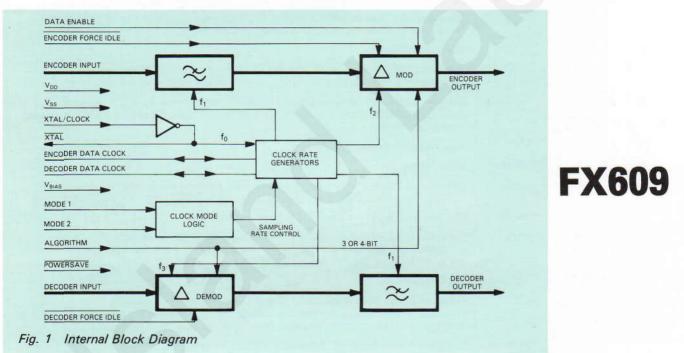

The FX609 is an LSI circuit designed as a Continuously Variable Slope Delta Modulation (CVSD) Codec and is intended for use in voice storage, time domain speech scramblers and digital speech communications equipment. Encode input and decoder output analogue filters are incorporated on-chip and use switched capacitor technology. Sampling clock rates can be programmed to 16, 32 or 64k bits/ second from an internal clock generator or may be externally applied in the range 8 to 64k bits/second. Sampling clock frequencies are output for the synchronisation of external circuits. The internal clocks are derived from an on-chip

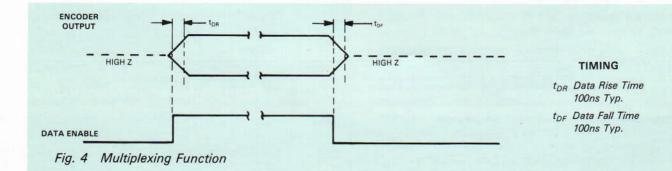

reference oscillator using an externally connected crystal. The encoder has an enable function for use in multiplexer applications. When not enabled, the encoder output is high impedance (three-state). Forced idle facilities in the encoder cause a perfect 1010...output pattern and in the decoder an output voltage of  $V_{DD}/2$ . The companding circuits may be operated with a 3 or 4-bit algorithm which is externally selected. The device may be put into standby mode by selection of the powersave facility. The FX609 is a low power, 5 volt CMOS device and is available in 22- pin DIL, 24-pin plastic quad or 28-pin PLCC packages.

## Pin Number

## Function

| DIL<br>FX609J | Quad<br>Plastic<br>FX609LG | PLCC<br>FX609LH |  |  |

|---------------|----------------------------|-----------------|--|--|

| 1             | 1                          | 1               |  |  |

|               | 2                          | 2               |  |  |

| 2             | 3                          | 3               |  |  |

| 3             | 4                          | 4               |  |  |

| 4             | 5                          | 5               |  |  |

|               |                            |                 |  |  |

| 5             | 6                          | 6               |  |  |

|               |                            |                 |  |  |

| 12.13         | 1.5                        |                 |  |  |

|               |                            |                 |  |  |

|               | CTAPLE                     | 7, 8            |  |  |

| 6             | 7                          | 9               |  |  |

|               |                            |                 |  |  |

| 7             | 8                          | 10              |  |  |

| 8             | 9                          | 11              |  |  |

| 9             | 10                         | 12              |  |  |

| 10            | 11                         | 13              |  |  |

| 10            |                            | 15              |  |  |

| 11            | 12                         | 14              |  |  |

| 12            | 13                         | 15,16           |  |  |

| 13            | 14                         | 17              |  |  |

| 14            | 15                         | 18,19           |  |  |

| 15            | 16                         | 20              |  |  |

|               |                            |                 |  |  |

|               | 17                         | 21              |  |  |

| 16            | 18                         | 22              |  |  |

|               |                            |                 |  |  |

| 17            | 19                         | 23              |  |  |

| 18            | 20                         | 24              |  |  |

| 19            | 21                         | 25              |  |  |

| 20            | 22                         | 26              |  |  |

| 20            | 22                         | 26              |  |  |

|               |                            |                 |  |  |

| -2-1-1-1      | -                          |                 |  |  |

|               |                            |                 |  |  |

|               |                            |                 |  |  |

|               |                            |                 |  |  |

|               |                            |                 |  |  |

|               |                            |                 |  |  |

| 22            | 24                         | 28              |  |  |

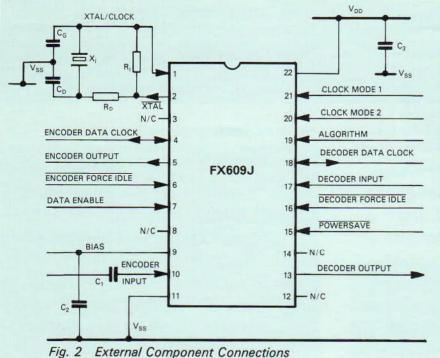

Xtal/Clock: Input to the clock oscillator inverter. A nominal 1.024MHz xtal input or externally derived clock is injected here. See Fig. 2.

#### No connection.

Xtal: Output of clock oscillator inverter.

#### No Connection.

**Encoder Data Clock:** A Logic I/O port. External encode clock input or internal data clock output. Clock frequency dependent upon clock mode 1, 2 inputs and xtal frequency (see **Clock Mode** pins).

Encoder Output: The encoder digital output, this is a three state output:

| Data Enable | Powersave | Encoder Output  |  |

|-------------|-----------|-----------------|--|

| 1           | 1         | Enabled         |  |

| 0           | 1         | High Z (o/c)    |  |

| 1           | 0         | V <sub>SS</sub> |  |

## No Connection.

**Encoder Force Idle:** When this pin is at logical '0' the encoder is forced to an idle state and the encoder digital output is 0101, a perfect idle pattern. When this pin is a logical '1' the encoder encodes as normal. Internal 1M $\Omega$  Pullup.

Data Enable: Data is made available at the encoder output pin by control of this input. See Encoder Output pin. Internal  $1M\Omega$  Pullup.

#### No Connection.

Bias: Normally at V<sub>DD</sub>/2 bias, this pin requires to be externally decoupled by a capacitor, C<sub>2</sub>. Internally pulled to V<sub>SS</sub> when "Powersave" is logical '0'.

**Encoder Input:** The analogue signal input. Internally biased at V<sub>DD</sub>/2, an external 1 $\mu$ F input coupling capacitor, C<sub>1</sub>, is required on this input. See Fig. 2 Note 3 for source impedance details.

Vss: Negative Supply (GND).

No connection.

**Decoder Output:** The recovered analogue signal is output at this pin, it is the buffered output of a low pass filter. During "Powersave" this output is o/c.

#### No Connection.

**Powersave:** A logical '0' at this pin puts most parts of the codec into a quiescent non-operational state. When at a logical '1' the codec operates normally. Internal  $1M\Omega$  Pullup.

#### No Connection.

**Decoder Force Idle:** A logical '0' at this pin gates a 0101...pattern internally to the decoder so that the Decoder Output goes to  $V_{DD}/2$ . When this pin is at a logical '1' the decoder operates as normal. Internal 1M $\Omega$  Pullup.

Decoder Input: Received digital signal input. Internal 1MQ Pullup.

**Decoder Data Clock:** A Logic I/O port. External decode clock input or internal data clock output, dependent upon clock mode 1, 2 inputs, see **Clock Mode** pins.

Algorithm: A logical '1' at this pin sets this device for a 3-bit companding algorithm. A logical '0' sets a 4-bit companding algorithm. Internal  $1M\Omega$  Pullup.

Clock Mode 2: These inputs select encoder and decoder data clock modes.

#### Clock Mode 1:

Intern 1MΩ μ

| al<br>pull-ups. | Clock<br>1 | Mode<br>2 |                                |

|-----------------|------------|-----------|--------------------------------|

|                 | 0          | 0         | External Clocks                |

|                 | 0          | 1         | Internal, $64kb/s = f \div 16$ |

|                 | 1          | 0         | Internal, $32kb/s = f \div 32$ |

|                 | 1          | 1         | Internal, $16kb/s = f \div 64$ |

Clock rates refer to f = 1.024MHz Xtal/Clock input.

During Internal Data Clock operation the data clock frequencies are available at the ports for external circuit synchronisation. Independent or Common data rate inputs to Encode and Decode data clock ports may be employed in the External Clocks mode.

V<sub>DD</sub>: Positive Supply: A single +5 volt power supply is required.

Component References

Component

Unit Value

Note

R1

Typ. 1 M

1

R0

Selectable

1

C1

1.0µ

2

C2

1.0µ

2

C3

1.0µ

2

C6

Typ. 33p

1

C6

Typ. 68p

1

X1

1.024 MHz

1, 2

#### Tolerance

Resistors  $\pm 10\%$ Capacitors  $\pm 20\%$

#### NOTES

Xtal circuitry shown is in accordance with CML application note D/XT/1 April '86.

A 1.024 MHz clock/xtal input will yield exactly 16/32/64 kb/s data clock rates.

3. To prevent unwanted internal oscillations at the encoder input pin, the source impedance to this input must be less than  $100\Omega$ . Output noise levels will improve with even lower source impedances.

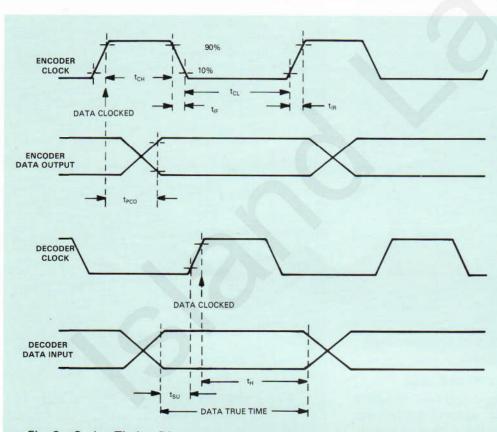

TIMING

t<sub>CH</sub> Clock '1' Pulse Widths 1μs Min.

t<sub>CL</sub> Clock '0' Pulse Widths 1μs Min.

t<sub>IR</sub> Clock Rise Time 100ns Typ.

t<sub>IF</sub> Clock Fall Time 100ns Typ.

t<sub>SU</sub> Data Set-up Time 450ns Max.

t<sub>H</sub> Data Hold Time 600ns Min.

$t_{SU} + t_H$  Data True Time  $t_{PCO}$  Clock to Output Delay Time = 750ns Max. Xtal input 1.024 MHz.

3

## **Specifications**

### **Absolute Maximum Ratings**

Exceeding the maximum rating can result in device damage. Operation of the device outside the operating limits is not implied.

| Supply voltage                                |            | -0.3V to 7.0V                    |  |  |

|-----------------------------------------------|------------|----------------------------------|--|--|

| Input voltage at any pin (ref V <sub>SS</sub> | = OV)      | -0.3 to (V <sub>DD</sub> + 0.3V) |  |  |

| Output sink/source current (sup               | ply pins)  | ±30mA                            |  |  |

| (othe                                         | er pins)   | ±20mA                            |  |  |

| Total device dissipation @ 25°C               |            | 800mW Max.                       |  |  |

| Derating                                      |            | 10mW/°C                          |  |  |

| Operating temperature range:                  | FX609J     | -30°C to +85°C (Ceramic)         |  |  |

|                                               | FX609LG/LH | - 30°C to + 70°C (Plastic)       |  |  |

| Storage temperature range:                    | FX609J     | -55°C to +125°C (Ceramic)        |  |  |

|                                               | FX609LG/LH | -40°C to +85°C (Plastic)         |  |  |

| <b>A</b>                                      |            |                                  |  |  |

## **Operating Limits**

All characteristics measured using the following parameters unless otherwise specified:

$V_{DD} = 5V$ ,  $T_{amb} = 25^{\circ}$ C, Xtal/Clock (f) = 1.024 MHz, Sample Rate 32kb/s.

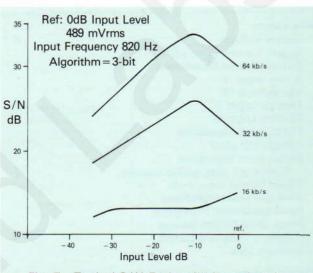

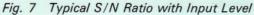

[Standard Test Signal 820Hz, ref. 0dB = 489mV (rms)]

| Characteristics                     | See Note | Min. | Тур.    | Max.                      | Unit     |

|-------------------------------------|----------|------|---------|---------------------------|----------|

| Static Values                       |          |      |         |                           |          |

| Supply Voltage                      | 1        | 4.5  | 5.0     | 5.5                       | v        |

| Supply Current (Enabled)            |          | _    | 3.5     | -                         | mA       |

| Supply Current (Powersave)          |          | -    | 500     |                           | μA       |

| Inputs Logic '1'                    |          | 3.5  | _       | _                         | V        |

| Inputs Logic '0'                    |          | _    | _       | 1.5                       | v        |

| Outputs Logic '1'                   |          | 4.0  |         | _                         | v        |

| Outputs Logic '0'                   |          | _    |         | 1.0                       | v        |

| Digital Input Impedance             |          |      |         | 1.0                       |          |

| (logic I/O pins)                    |          | -    | 10      | _                         | MΩ       |

| Digital Input Impedance             |          |      | 10      |                           | TVIGE    |

| (logic input pins, pullup resistor) | 2        | 300  |         | -                         | kΩ       |

| Digital Output Impedance            | -        | _    | 4       |                           | kΩ       |

| Analogue Input Impedance            |          | _    | 100     | <u></u>                   | kΩ       |

| Analogue Output Impedance           |          | _    | 800     | _                         | Ω        |

| Three State Output leakage          |          |      | 000     |                           |          |

| Current (output disabled)           |          | _    | $\pm 4$ |                           | μA       |

| Insertion Loss                      |          | -    | 0       |                           | dB       |

|                                     |          |      | 0       |                           | ub       |

| Dynamic Values                      | 1        |      |         |                           |          |

| Encoder:                            |          |      |         |                           |          |

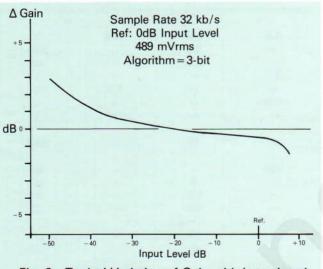

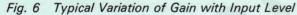

| Analogue Signal Input levels        | 5        | - 30 | _       | +8                        | dB       |

| Principal Integrator Frequency      |          | _    | 275     | 200 - Harrison - Harrison | Hz       |

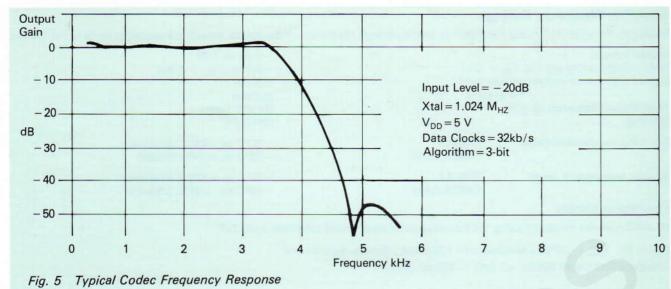

| Encoder Passband                    |          |      | 3400    |                           | Hz       |

| Compand Time Constant               |          | -    | 4       | _                         | ms       |

| Decoder:                            |          |      |         |                           |          |

| Analogue Signal Output levels       | 5        | - 30 | -       | +8                        | dB       |

| Decoder Passband                    |          | 300  | -       | 3400                      | Hz       |

| Encoder Decoder (Full codec):       |          |      |         |                           |          |

| Passband                            |          | 300  |         | 3400                      | Hz       |

| Stopband                            |          | 6    | _       | 10                        | kHz      |

| Stopband Attenuation                |          | _    | 60      | -                         | dB       |

| Passband Gain                       |          | _    | 0       | _                         | dB       |

| Passband Ripple                     |          | -3   | U       | +3                        | dB       |

| Output Noise (Input short circuit)  |          | _    | - 60    | + 3                       | dB       |

| Perfect Idle Channel Noise          |          | _    | -00     |                           | uв       |

| (Encode Forced)                     |          | -    | - 63    |                           | dB       |

| Group Delay Distortion              | 3        |      | -05     |                           | UD       |

| 1000 – 2600Hz                       | 0        | _    |         | 450                       |          |

| 600 - 2800Hz                        |          |      |         | 750                       | μs       |

| 500 - 3000Hz                        |          |      | _       | 1.5                       | μs<br>ms |

| Xtal/Clock Frequency                |          | 500  | 1024    | 1500                      | kHz      |

Notes: 1. Dynamic characteristics specified at 5V only.

2. All logic Inputs except, Encoder and Decoder Data Clocks.

3. Group delay distortion for full codec relative to the delay at 820Hz, -20dB at the encoder input.

4. Relative timings are shown on Figures 3 and 4. 5. Recommended values-see graph Fig. 7.

3

## **Codec Performance**

Ti Fi ar To ar pi fo

fre

P

Fi

С

E

F

F

## Package Outlines

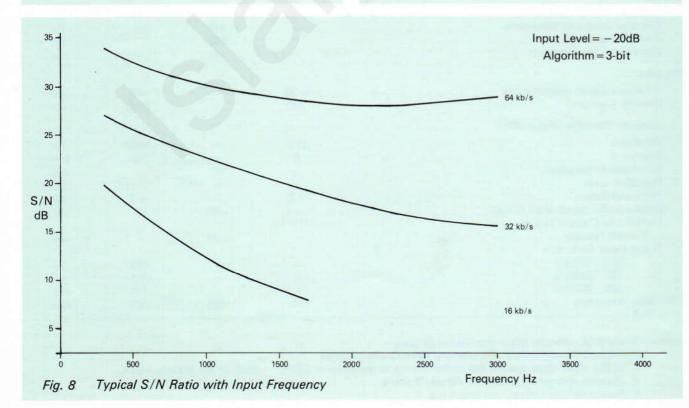

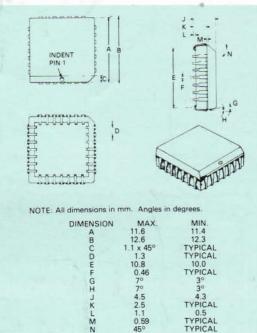

The FX609J, the cerdip package, is illustrated in *Figure 9*. The 'LG' version is shown in *Figure 10*, and the 'LH' version in *Figure 11*.

To allow complete identification, the FX609 LG and LH packages have an indent spot adjacent to pin 1 and a chamfered corner between pins 3 and 4 for LG package, between pins 4 and 5 for LH package. Pins number anti-clockwise when viewed from the top (indent side).

#### B PIN 1 H G D NOTE: All dimer sions in mm DIMENSION MAX. MIN. 27.38 9.75 10.60 26.98 9.55 AB 10.40 25.30 CD 25.50 2.54 0.46 4.35 EFGH TYPICAL 4.27 3.99

## Fig. 9 FX609J 22-pin DIL Package

**Ordering Information**

carrier.

22-pin cerdip DIL

bent and cropped.

24-pin guad plastic encapsulated,

28-lead Plastic leaded chip

FX609J

**FX609LG**

**FX609LH**

The FX609J/LG/LH is a CMOS LSI circuit which includes input protection. However, precautions should be taken to prevent static discharges which may cause damage.

## Fig. 10 FX609LG 24-pin Package

## Fig. 11 FX609LH 28-lead Package

CML does not assume any responsibility for the use of any circuitry described. No circuit patent licences are implied and CML reserves the right at any time without notice to change the said circuitry.

## CONSUMER MICROCIRCUITS LIMITED

1 WHEATON ROAD  $\cdot$  INDUSTRIAL ESTATE EAST WITHAM  $\cdot$  ESSEX CM8 3TD  $\cdot$  ENGLAND

Telephone: (0376) 513833 Telex: 99382 CMICRO G Telefax: (0376) 518247

© 1988 Consumer Microcircuits Limited