# **CML Semiconductor Products**

PRODUCT INFORMATION

# FX621 Low-Power Subscriber Private Metering (SPM) Detector

With compliments of Island Labs

Publication D/621/1 June 1989 Provisional Issue

# Features/Applications

- Meets 12kHz and 16kHz SPM Specifications

- Low-Power CMOS [ 3 5 Volt Operation ]

- Tone Follower and SPM Packet Detection Modes

- Adjustable Input Gain

- PABX , Payphone and Telephone Applications

- General Purpose Tone Detection

- Surface Mount and DIL Package Styles

- Crystal Oscillator Stability

FX621

# **Brief Description**

The FX621 is a single-chip, low-power CMOS tone detector designed for use in both PABX and general payphone applications for Subscriber Private Metering.

The Decode and Not-Decode band edges are accurately defined by the use of an external

4.433619MHz crystal.

Operation to either of the 12kHz or 16kHz SPM systems is pin programmable, with system amplitude sensitivities and pulse length timing being provided by the use of external components.

The FX621 has 2 pin-selectable modes of operation:

- Tone Follower Mode.

- 2) SPM Packet Mode.

Tone Follower Mode.

A logic "0" is output whenever a tone of the correct frequency and length is detected.

SPM Packet Mode.

An output is obtained only when both the mark and space timing criteria of an input SPM tone have been fulfilled.

This device, which is available in plastic DIL and SMD packages, requires only a single 3-volt (minimum) power supply, a 4.433619MHz crystal with external gain and timing components to meet most SPM specifications.

| DII           | Ound               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|---------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| DIL<br>FX621P | Quad<br>FX621LG/LS |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 1             | 1                  | Xtal/Clock: Input to the clock oscillator inverter. A single 4.433619MHz Xtal or external clock pulse input is required (see Figure 2).                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| 2             | 2                  | V <sub>DD</sub> : The positive supply rail. A single, stable supply in the range 3V to 5V is required.                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

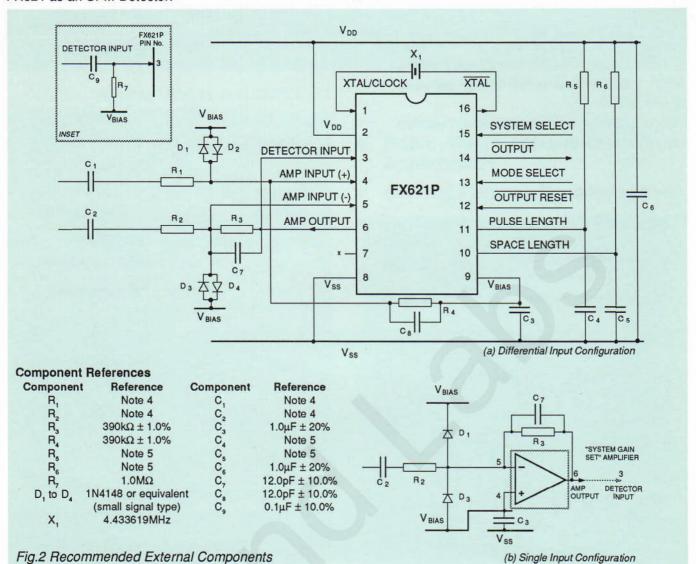

| 3             | 5                  | <b>Detector Input :</b> "Schmitt Trigger" level detector circuitry whose input thresholds are set internally and dependent on the applied $V_{DD}$ . For use with low signal level systems this input should be preceded by the "System Gain Set" amplifier. To use this input without the "System Gain Set" amplifier, the components indicated in Figure 2 (inset) should be used with the protection diodes ( $D_1 - D_4$ ).                                                                   |  |  |  |  |  |  |

| <b>4 5</b>    | 7                  | Amplifier Input (+): Amplifier. With single or differential inputs this amplifier and its external circuitry can be used to provide the extra gain required to set the device to the user's National Level Specification.  External diodes are used at both inputs (if in use) to provide protection when the line input level exceeds the supply rails (above the Absolute Maximum Rating). If this device is  Amplifier Input (-): used without this amplifier, the protection diodes should be |  |  |  |  |  |  |

|               |                    | employed at the Detector Input. See Figure 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

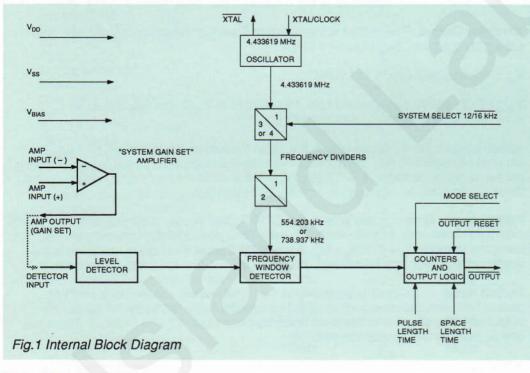

| 6             | 8                  | <b>Amplifier Output:</b> The output of the "System Gain Set" Amplifier, is used with gain setting components. See Figures 1 and 2.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 8             | 12                 | V <sub>ss</sub> : The negative supply rail, (GND).                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 9             | 13                 | $ m V_{BIAS}$ : The internal analogue bias pin, this point is at $\rm V_{DD}/2$ and requires to be externally decoupled to $\rm V_{SS}$ via capacitor $\rm C_3$ .                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| 10            | 14                 | <b>Space Length Time</b> : Active only in the 'SPM Packet' mode, this input, with an external RC network, sets the minimum valid No-Tone (Space) period for the incoming packet using the formula: $t_s = 0.7$ ( $R_6 \times C_5$ ). If the 'SPM Packet' mode is not required these timing components may be omitted. See page 4.                                                                                                                                                                 |  |  |  |  |  |  |

| 11            | 17                 | <b>Pulse Length Time:</b> Active only in the 'SPM Packet' mode, this input, with an external RC network, sets the minimum valid Tone period for the incoming packet using the formula: $t_M = 0.7  (R_5 \times C_4)$ . If the 'SPM Packet' mode is not required these timing components may be omitted. See page 4.                                                                                                                                                                               |  |  |  |  |  |  |

| 12            | 18                 | Output Reset: This input is used only in the 'SPM Packet' mode. Once an SPM packet has been detected and an output generated (logic "0") from this device the output remains as set until this input is strobed to a logic "0." See Figure 3. This input has an internal $1M\Omega$ pullup resistor.                                                                                                                                                                                              |  |  |  |  |  |  |

| 13            | 19                 | <b>Mode Select</b> : A control pin to select either the 'Tone Follower' mode or the 'SPM Packet' mode. A logic "1" selects 'Tone Follower', a logic "0" selects 'SPM Packet.' This input has an internal $1M\Omega$ pullup resistor (Tone Follower).                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| 14            | 20                 | Output: The digital output of the SPM Detector. In the 'Tone Follower' mode a valid tone gives a logic "0" and no-tone gives a logic "1." Tonebursts and tone dropouts of less than 16 cycles are ignored. In the 'SPM Packet' mode the output is set to a logic "0" when a valid 'packet' is measured. The output remains as set until reset by a logic "0" at the Output Reset function, see Figure 3.                                                                                          |  |  |  |  |  |  |

| 15            | 23                 | System Select: A control pin to set the device to work on either a 12kHz (logic "1") or 16kHz (logic "0") SPM system. This input has an internal $1M\Omega$ pullup resistor (12kHz).                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| 16            | 24                 | Xtal: The output of the clock oscillator inverter, see Figure 2.                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|               | 3, 4, 9, 10,       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

## **Application Information**

The notes on these pages are intended to assist in calculating the external components required to operate the FX621 as an SPM Detector.

# **Gain Component Calculations**

(1) Calculate the FX621 sensitivity.

Device Sensitivity – at the Detector Input (Figure 1) is dependent upon the V<sub>DD</sub> value and is calculated as:

Device Sensitivity

$$\approx \frac{0.2 \times V_{DD}}{2 \times \sqrt{2}}$$

(Vrms)

- (2) Ascertain the required National (Minimum Will-Decode) and [Maximum Will-Not Decode] Levels.

- (3) Calculate the acceptable range of required Gain/Attenuation for the levels in Note 2, using the "System Gain Set" amplifier.

The gain requirement is calculated as:

Choose a gain figure that meets both level requirements.

(4) Calculate the gain/attenuation components for the chosen gain.

Gain Components - for a differential input:

This calculation approximates as:

$$R_1 \approx \frac{R_4}{1.2 \text{ x (selected gain)}}$$

and

$$C_1 \approx \frac{1}{2\pi \times R_1 \times 6.0 \text{kHz}}$$

– using the nearest preferred value components. The values of  $\rm R_1$  and  $\rm C_1$  have been calculated to give a high-pass cut-off between the audio and SPM tone frequencies, approximately 6kHz.  $\rm C_7$  and  $\rm C_8$  are antialias components and are calculated for an approximate cut-off frequency of 32kHz.

# Application Information .....

#### (5) Timing Components

In the 'SPM Packet' mode  $R_5$  and  $C_4$  set the minimum 'Tone' period  $(t_M)$ ,  $R_6$  and  $C_5$  set the minimum 'Space' period  $(t_S)$ , and are calculated as follows:

$$t_M = 0.7(R_5 \times C_4).$$

$t_S = 0.7(R_6 \times C_5).$

When calculating Tone and Space time settings the following points should be taken into consideration:

- (1) Response and De-response times  $t_R$  and  $t_D$ .

- (2) Component tolerances can alter the calculation.

- (3) The MINIMUM expected pulse/space length must be catered for.

#### (6) Protection Diodes

As most telephone systems operate at voltages in excess of the Absolute Maximum Limits for damage, diodes  $D_1 - D_4$  are essential for device protection.

#### (7) Component Tolerances

The tolerances of external components used with this device are dependent upon the required accuracy of the gain and pulse period timings.

#### **Timing**

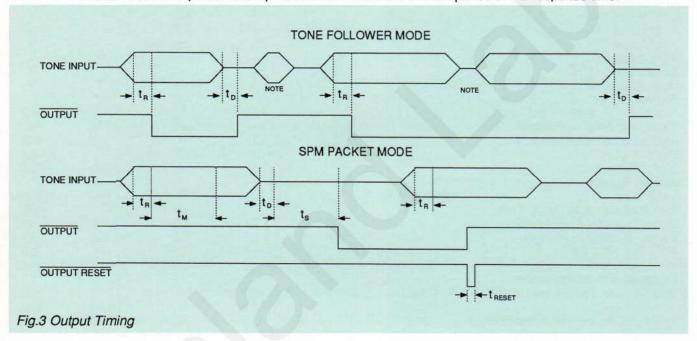

Figure 3 shows the FX621 output timing – Timing value limits are given on the "Specification" page.

Note – There is no reaction to pulses or drop-outs of less than the valid Response or De-response time.

# Example Values - for the FX621 to operate with the West German (16kHz) 'FTZ' Specification.

(a) Min. 'Will Decode' Level 71.3 mV rms (b) Max. 'Will Decode' Level 10.0 V rms (c) Max. 'Will-Not Decode' Level 34.6 mV rms (d) Device Sensitivity @ 3.0V VDD 212.0 mV rms Min. Gain Required (d+a)3.0 Max. Gain Allowed (d+c) 6.1 Chosen Gain Figure 4.0

For a chosen gain figure of 4.0, a minimum Tone length of 80ms, a minimum Space length of 135ms and a  $V_{\rm DD}$  of 3.0 V, the required component values are :

| R <sub>1</sub> | 82kΩ        | C,                               | 330pF |

|----------------|-------------|----------------------------------|-------|

| R,             | 82kΩ        | C,                               | 330pF |

| R <sub>3</sub> | 390kΩ       | C <sub>3</sub>                   | 1.0µF |

| R,             | 390kΩ       | C <sub>4</sub>                   | 820nF |

| R <sub>5</sub> | 100kΩ       | C <sub>5</sub>                   | 1.0µF |

| R <sub>6</sub> | 120kΩ       | C                                | 1.0µF |

|                |             | C <sub>6</sub><br>C <sub>7</sub> | 12pF  |

| X,             | 4.433619MHz | C's                              | 12pF  |

Tolerances: Resistors =  $\pm 1\%$ . Capacitors =  $\pm 10\%$ .

# Specification

#### Absolute Maximum Ratings

Exceeding the maximum rating can result in device damage. Operation of the device outside the operating limits is not implied.

| Supply Voltage                                      | -0.3 to 7.0V                |  |  |  |

|-----------------------------------------------------|-----------------------------|--|--|--|

| Input Voltage at any pin (ref V <sub>SS</sub> = 0V) | $-0.3$ to $(V_{DD} + 0.3V)$ |  |  |  |

| Sink/source current (supply pins)                   | ± 30mA                      |  |  |  |

| (other pins)                                        | ± 20mA                      |  |  |  |

| Total device dissipation @ T <sub>AMB</sub> 25°C    | 800mW Max.                  |  |  |  |

| Derating                                            | 10mW/°C                     |  |  |  |

| Operating temperature range: FX621P/LG/LS           | -30°C to + 70°C             |  |  |  |

| Storage temperature range: FX621P/LG/LS             | -40°C to + 85°C             |  |  |  |

#### **Operating Limits**

All device characteristics are measured under the following conditions unless otherwise specified:

$V_{DD} = 3.0V$   $T_{AMB} = 25$ °C Xtal/Clock  $f_{c} = 4.433619$ MHz Audio level 0dB ref = 775mV rms

| Characteristics                                                        | System           | See Note     | Min.               | Тур.     | Max.  | Unit      |

|------------------------------------------------------------------------|------------------|--------------|--------------------|----------|-------|-----------|

| Static Values                                                          |                  |              |                    |          |       |           |

| Supply Voltage (V <sub>DD</sub> )                                      |                  |              | 2.8                | 3.0      | 5.0   | V         |

| Supply Voltage (V <sub>DD</sub> )<br>Supply Current (I <sub>DD</sub> ) |                  |              | -                  | 1.0      | _     | mA        |

| Input Logic "1"                                                        |                  | 2            | 2.1                | _        | _     | V         |

| Input Logic "0"                                                        |                  | 2            | ( ) <del>-</del> A | _        | 0.9   | V         |

| Output Logic "1"                                                       |                  | 2<br>2<br>2  | 2.4                | _        | _     | V         |

| Output Logic "0"                                                       |                  | 2            | _                  | _        | 0.6   | V         |

| Impedances                                                             |                  |              |                    |          |       |           |

| "Gain Set" Amplifier Input                                             |                  |              | 1.0                | _        | -     | $M\Omega$ |

| "Gain Set" Amplifier Output                                            |                  |              | _                  | -        | 10.0  | kΩ        |

| Analogue Detector Input                                                |                  |              | 1.0                | _        | _     | $M\Omega$ |

| Digital Inputs                                                         |                  |              | _                  | 1.0      | _     | MΩ        |

| Digital Output                                                         |                  |              | _                  | _        | 10.0  | kΩ        |

| Dynamic Values                                                         |                  |              |                    |          |       | 1122      |

| Sensitivity                                                            | 12kHz/16kHz      | 1, 2         | _                  | 212.0    |       | mV rms    |

| Required Signal to Noise Ratio                                         | 12/11/22/10/11/2 | 7            | _                  | 45       | _     | dB        |

| Upper Detector Threshold                                               |                  | 2            | 1.77               | 1.8      | 1.83  | V         |

| Lower Detector Threshold                                               |                  | 2 2          | 1.17               | 1.2      | 1.23  | v         |

| Amplifier Input Offset                                                 |                  | _            |                    | 15.0     | _     | mV        |

| Xtal Oscillator Frequency                                              |                  |              |                    | 4.433619 |       | MHz       |

| Frequency Discrimination                                               |                  |              |                    | 1.100010 |       | 1411 12   |

| 'Will-Decode' Frequency Limits                                         | 12kHz            |              | 11.82              |          | 12.18 | kHz       |

| Will Decode Trequency Elithis                                          | 16kHz            |              | 15.76              |          | 16.24 | kHz       |

| 'Will-Not Decode' Frequency Limits                                     | 12kHz            |              | 0                  |          | 11.52 | kHz       |

| Will-Not Decode Trequency Limits                                       | 12kHz            |              | 12.48              |          | 11.52 | kHz       |

|                                                                        | 16kHz            |              | 0                  | 100      | 15.36 | kHz       |

|                                                                        | 16kHz            |              | 16.64              |          | 15.50 | kHz       |

| Timing Information - Fig.3                                             | TONTIZ           |              | 10.04              | _        | _     | KIIZ      |

| Valid Tone Burst Length (t,,)                                          | 12/16kHz         | 2.4          | 16.0               |          |       | ovelee    |

|                                                                        |                  | 3, 4         |                    |          |       | cycles    |

| Valid Space Length (t <sub>s</sub> )                                   | 12/16kHz         | -4-7         | 5.0                |          |       | ms        |

| Tone Response Time (t <sub>R</sub> )                                   | 12kHz            | 5, 7         | _                  | 1.7      | 3.0   | ms        |

| Do roopenso Time (t.)                                                  | 16kHz            | 5, 7<br>6, 7 | _                  | 1.2      | 2.0   | ms        |

| De-response Time (t <sub>D</sub> )                                     | 12kHz            | 6, 7         | -                  | 1.7      | 3.0   | ms        |

| CDM Output Deast Time #                                                | 16kHz            | 6, 7         | 450.0              | 1.2      | 2.0   | ms        |

| SPM Output Reset Time (t <sub>RESET</sub> )                            | 12/16kHz         | 4            | 150.0              | _        | _     | ns        |

#### **Notes**

- Device sensitivity at the Detector Input pin, or using the 'Gain Set' Amplifier at unity.

- These values are quoted at 3-volt V<sub>DD</sub>, any supply variation will alter levels accordingly.

Tone Follower mode.

- 4. SPM Packet mode, in this mode the minimum valid Pulse (Space) length is programmable by means of an RC network on the Pulse (Space) Length Time pin. If no RC network is used, the minimum valid tone length reverts to 16 cycles.

- The time for the circuit to recognize a valid 'Tone' in the Tone Follower mode.

6. The time for the circuit to recognize a valid 'No Tone' in the Tone Follower mode.7. The FX621 is a low-power zero crossing detector without on-chip filtering, for use with a good Signal-to-Noise ratio. The FX611 is recommended for high noise environments. If the supply current requirement of the FX611 is unacceptable, separate external filters should be employed with the FX621.

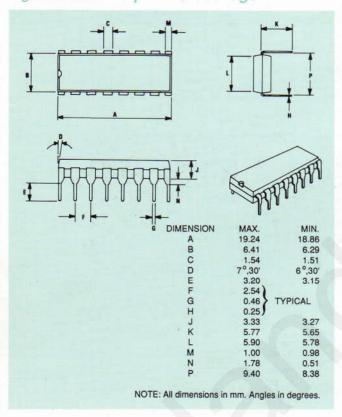

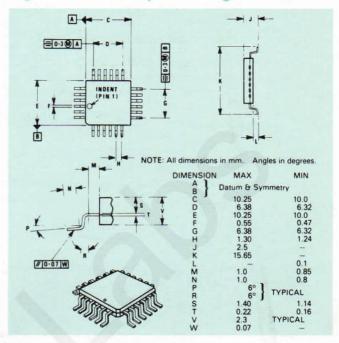

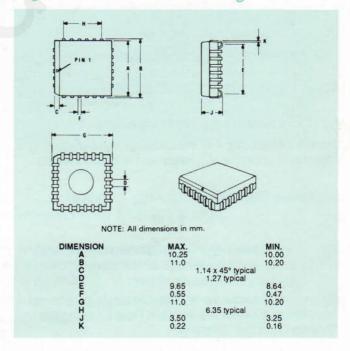

## Package Outline

The FX621P package is shown in Figure 4. The 'LG' version is shown in Figure 5, and the 'LS' version in Figure 6.

To allow complete identification, the 'LG' and 'LS' packages have an indent spot adjacent to pin 1 and a chamfered corner between pins 3 and 4.

Pins number anti-clockwise when viewed from the top (indent side).

Fig.4 FX621P 16-pin DIL Package

# **Ordering Information**

FX621P 16-pin plastic DIL

FX621LG 24-pin quad plastic

encapsulated bent and

cropped

FX621LS 24-lead plastic leaded chip

carrier

# **Handling Precautions**

The FX621 is a CMOS LSI circuit which includes input protection. However precautions should be taken to prevent static discharges which may cause damage.

Fig. 5 FX621LG 24-pin Package

Fig. 6 FX621LS 24-lead Package

CML does not assume any responsibility for the use of any circuitry described. No circuit patent licences are implied and CML reserves the right at any time without notice to change the said circuitry.

# CONSUMER MICROCIRCUITS LIMITED