SP8605 1GHz Counter

Features

- ECL Compatible Outputs

- AC Coupled Inputs (Internal Bias)

- Temperature Range: -55°C to +125°C (A Grade)

Quick Reference Data

- Supply Voltage: -5.2V

- Power Consumption: 320mW

- Input Frequency: 1GHz

Description

The SP8605 UHF counter is fixed ratio, divide by two, asynchronous emitter coupled logic counter with a maximum operating frequency in excess of 1GHz, over a temperature range of 0° C to 70° C (B Grade) and -40° C to +85° C (M grade). The input is capacitively coupled to the signal source but can be DC coupled if it is required. The two complementary emitter follower outputs are capable of driving 100 ohm lines and interfacing to ECL with the same positive supply. The SP8605 require supplies of 0V and -5.2V ±0.25V).

Operating Notes

The SP8605 divider is very simple to use but normal high frequency rules should be followed for optimum performance, for example, all connections should be kept short, the capacitors and resistors should be types suitable for the frequencies involved.

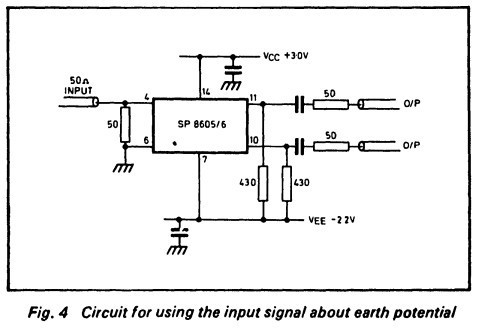

The input is generally capacitively coupled to the signal source. There is an internal 400 ohm resistor connecting the input to a reference voltage; this biases the input in the middle of the transfer characteristic. The reference voltage is brought out onto pin 6, which should be decoupled to the earth plane. This decoupling completes the input signal path to the device and therefore must be very low inductance for optimum performance. The sensitivity of the device can be increased by DC coupling the input signal about earth (see Fig. 4).

VCC - VEE should be kept inside the specified 5.2 volts ± 0.25 volts but the actual value of Vee relative to earth is not very critical and can be varied between 2.7V and 3.3V with only a small effect on performance. A VEE of about 3.0V is the optimum for full temperature range operation.

In the absence of an input signal both the DC coupled and the capacitively coupled circuits will self oscillate with an output frequency of approximately 400MHz. This can be prevented by connecting a 10 kohm resistor between the input and the negative rail. This offsets the input sufficiently to stop the oscillation but it also reduces the input sensitivity by approximately 100mV.

The SP8605 will incorrectly count low frequency sinusoidal inputs with slow ramps. A response rate of 200 V/µs or higher is required for safe low frequency operation.

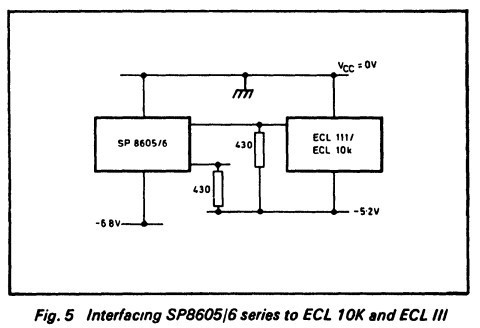

The output can be interfaced to ECL 10K or ECL III (See Fig. 5.). The unused output should be connected to a load resistor as shown to reduce output distortion.

The input impedance of the SP8605 is a function of frequency and minimises at about the same frequency as the maximum input sensitivity, so, although it can load the signal source significantly there is generally enough signal to operate the device satisfactorily when the input impedance is at a minimum. The worst case occurs at the maximum frequency because this is where the input sensitivity is worst.

The input is generally capacitively coupled to the signal source. There is an internal 400 ohm resistor connecting the input to a reference voltage; this biases the input in the middle of the transfer characteristic. The reference voltage is brought out onto pin 6, which should be decoupled to the earth plane. This decoupling completes the input signal path to the device and therefore must be very low inductance for optimum performance. The sensitivity of the device can be increased by DC coupling the input signal about earth (see Fig. 4).

VCC - VEE should be kept inside the specified 5.2 volts ± 0.25 volts but the actual value of Vee relative to earth is not very critical and can be varied between 2.7V and 3.3V with only a small effect on performance. A VEE of about 3.0V is the optimum for full temperature range operation.

In the absence of an input signal both the DC coupled and the capacitively coupled circuits will self oscillate with an output frequency of approximately 400MHz. This can be prevented by connecting a 10 kohm resistor between the input and the negative rail. This offsets the input sufficiently to stop the oscillation but it also reduces the input sensitivity by approximately 100mV.

The SP8605 will incorrectly count low frequency sinusoidal inputs with slow ramps. A response rate of 200 V/µs or higher is required for safe low frequency operation.

The output can be interfaced to ECL 10K or ECL III (See Fig. 5.). The unused output should be connected to a load resistor as shown to reduce output distortion.

The input impedance of the SP8605 is a function of frequency and minimises at about the same frequency as the maximum input sensitivity, so, although it can load the signal source significantly there is generally enough signal to operate the device satisfactorily when the input impedance is at a minimum. The worst case occurs at the maximum frequency because this is where the input sensitivity is worst.

Applications

The SP8605 can be used in instrumentation for direct counting applications up to 1.3GHz and in frequency synthesisers.