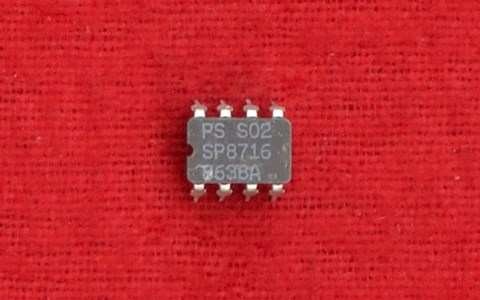

SP8716 Counter

Features

- DC to 520MHz Operation

- -40°C to +85°C Temperature Range

- Control Inputs and Outputs are CMOS Compatible

Quick Reference Data

- Supply Voltage 5.0V ± 0.25V

- Supply Current 10.5mA typical

- Storage temperature range: -55°C to +150°C

Description

The SP8716 is a divide by 40/41, programmable dividers with a maximum specified operating frequency of 520MHz over the temperature range -40 °C to + 85 °C.

The signal (clock) inputs are biased internally and require to be capacitor coupled. The output stage is of an unusual low power design featuring dynamic pull-up and optimised for driving CMOS. The 0 to 1 output edge should be used to give the best loop delay performance.

Operating

- The inputs are biased internally and coupled to a signal source with suitable capacitors.

- If no signal is present the devices will self-oscillate. If this is undesirable, it may be prevented by connecting a 15k resistor from one input to pin 4 (ground). This will reduce the sensitivity.

- The circuits will operate down to DC, but slew rate must be better than 100V/µs.

- The output stage is of an unusual design and is intended to interface with CMOS. External pull-up resistors or circuits must not be used.

- This device is NOT suitable for driving TTL or its derivatives.